Delta-Sigma prevodníky

| Predmet |

|

|---|---|

| Konfigurovateľné mikroprocesorové systémy | |

| Tématická časť: | |

| Analógové spracovanie signálov |

Delta-Sigma (Δ-Σ), resp. Sigma-Delta (Σ-Δ) prevodníky sú moderné prevodníky, pracujúce na princípe Σ-Δ modulátora, vyznačujúce sa jednoduchým hardvérom, ale zložitým softvérom pracujúcim ako signálový procesor. Hoci princíp Σ-Δ prevodu je známy už viac desiatok rokov, jeho širšie využitie bolo možné až keď sa dostatočne rozvinula technológia výroby integrovaných obvodov s veľmi vysokou hustotou integrácie umožňujúca jeho praktickú realizáciu.

Základná koncepcia Sigma-delta prevodníka:

- prevzorkovanie meraného signálu (oversampling)

- tvarovanie spektra (noise shaping)

- číslicová filtrácia (digital filtration)

- decimácia (decimation)

Obsah

Transformácia Δ-modulátora na Σ-Δ-modulátor

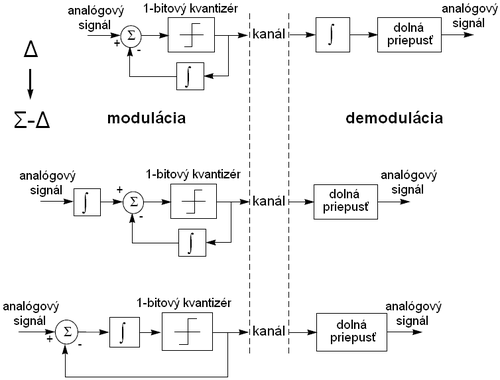

Sigma-delta modulátor je rozšírením delta modulátora. Delta modulácia využíva dva integrátory. Pretože integrácia je lineárna operácia, je možné druhý integrátor presunúť pred modulátor bez vplyvu na celkovú činnosť dvojice modulátor-demodulátor. Naviac je možné integrátory presunúť za uzol a vytvoriť sigma-delta modulátor, ktorého štruktúra ako aj princíp transformácie delta modulátora na sigma-delta modulátor je znázornený na Obr.1.

Popis činnosti Σ-Δ prevodníka

Prevzorkovanie znamená AČ prevod podstatne vyššou rýchlosťou ako vyžaduje vzorkovacia teoréma. Pri tvarovaní spektra dochádza k potlačeniu digitalizačného šumu. Číslicová filtrácia znamená v najjednoduchšom prípade výpočet aritmetického priemeru z viacerých výsledkov prevodu, čím sa zároveň zvyšuje jeho rozlišovacia schopnosť. Pri decimácii sa znižuje frekvencia výstupných údajov prevodníka na hodnotu zodpovedajúcu vzorkovacej teoréme.

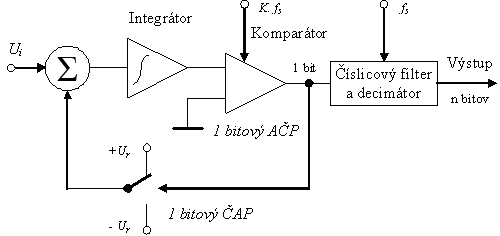

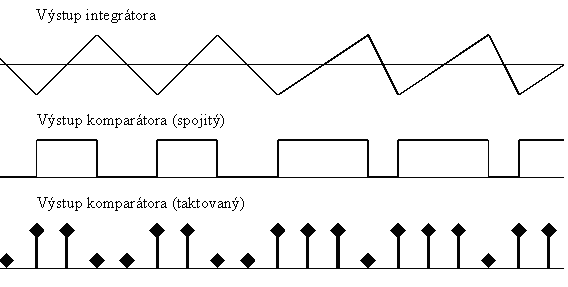

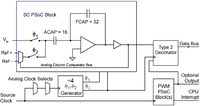

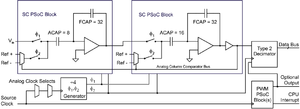

Vstupné napätie, ku ktorému je pripočítaný výstup 1-bitového ČA prevodníka, je privedené na integrátor. Výstup integrátora sa porovnáva s nulovým napätím komparátorom, ktorý môžeme nazvať aj 1-bitovým AČ prevodníkom. Výstup komparátora, ktorý je taktovaný frekvenciou K.fs, kde K je koeficient prevzorkovania a fs je výstupná frekvencia údajov AČ prevodníka, je vstupom prepínača v spätnej väzbe, ktorý tvorí 1-bitový ČA prevodník. Táto časť prevodníka sa nazýva Σ-Δ modulátor. Jeho výstupom je jednobitový prúd s frekvenciou K.fs.

Číslicový dolnopriepustný filter v podstate počíta plávajúci priemer z mnohých jednobitových výstupov Σ-Δ modulátora a tým zvyšuje rozlišovaciu schopnosť prevodníka. Ak by sme len takto chceli dosiahnuť n-bitový nárast rozlíšenia, potrebovali by sme použiť koeficient prevzorkovania 2n. V prípade Σ-Δ modulátora však dochádza k tvarovaniu spektra kvantizačného šumu tak, že sa presúva mimo priepustné pásmo dolnopriepustného filtra, čo spôsobuje oveľa vyšší nárast ekvivalentného počtu bitov než vyplýva zo samotného prevzorkovania.

Filtrovanie zároveň znižuje frekvenčný rozsah signálu, takže frekvencia K.fs je podstatne vyššia než vyžaduje vzorkovacia teoréma. Posledným krokom sigma-delta prevodu je preto decimácia – vynechanie „zbytočných“ údajov. Na výstup AČP je privedený len každý K-ty údaj. Decimácia nespôsobuje žiadnu stratu informácie. Výstup Σ-Δ AČ prevodníka má teda n bitov s frekvenciou „vzorkovania“ fs.

Výhodou sigma-delta AČP je najmä to, že vďaka veľkému prevzorkovaniu väčšinou nepotrebujú protiprekryvný (antialias) filter, majú vynikajúcu linearitu, nepotrebujú vzorkovací obvod (S&H) a ich vlastnosti (šírka pásma filtra, opakovacia frekvencia výstupu, dynamický rozsah) sa nastavujú hodinovou frekvenciou fs. Nevýhodou je, že potrebujú istý čas (asi 4 AČ prevody) na ustálenie a teda sa nehodia na multiplexný režim. Aby sa ich veľká rozlišovacia schopnosť a linearita dala využiť, ich súčasťou sú autokalibračné obvody, ktoré zabezpečujú aj malú chybu prevodu.

Najpresnejšie sigma-delta AČP dosahujú rozlišovaciu schopnosť 24 bitov pri niekoľkých desiatkach až stovkách prevodov za sekundu. Iná skupina týchto prevodníkov sa používa v audio aplikáciách; tieto majú rozlišovaciu schopnosť 16 bitov pri 48 tisíc prevodoch za sekundu.

Výhody Σ-Δ prevodníkov

- Kompatibilita s technológiou VLSI (90 % obvodov prevodníka je realizovaných číslicovou technikou), čo umožňuje integráciu týchto prevodníkov spolu s obvodmi DSP na jednom čipe.

- Nízka cena týchto prevodníkov vychádza predovšetkým z predchádzajúcej vlastnosti, prispieva však k nej aj skutočnosť, že zvyšná časť analógových obvodov nevyžaduje vysokú presnosť (nie sú nevyhnutné presné obvody ani laserové trimovanie).

- Vysoká linearita je garantovaná princípom činnosti.

- Podstatne nižšie nároky na vstupný (obmedzovací) a výstupný (rekonštrukčný) analógový filter, ktoré sú zvyčajne súčasťou kompletného systému ČSS.

Tieto vlastnosti sigma-delta prevodníkov sú prakticky opakom nevýhodných vlastností konvenčných prevodníkov, čo im zabezpečuje široké možnosti využitia. Základnou nevýhodou sigma-delta prevodníkov je ich relatívne nízka výstupná frekvencia vzorkovania, čo obmedzuje ich využitie v systémoch ČSS s maximálnou frekvenciou vzorkovania rádovo 100ky KHz.

Delta-Sigma prevodníky v programe Cypress

Množstvo PSoC (Programmable System-on-Chip) aplikácií využíva A/D prevodník (ADC). PSoC Designer poskytuje desiatky A/D prevodníkov s rôznym rozlíšením, vzorkovacou frekvenciou, pomermi signál/šum (SNR) a využitím zdrojov.

Definícia základných parametrov

Rozsah – je rozdiel medzi minimálnou a maximálnou hodnotou nameranou A/Dprevodníkom.

Rozlíšenie – je rozdiel medzi po sebe idúcimi nameranými hodnotami, určený rozsahom A/D prevodníka vydeleným počtom výsledkov, typicky 2n-1. Napr. 10-bit A/D prevodník s rozsahom 5.0V má rozlíšenie 5,0 V/1023 = 4,89 mV na 1bit.

Vzorkovací frekvencia – udáva počet prevodníkom získaných vzoriek za sekundu.

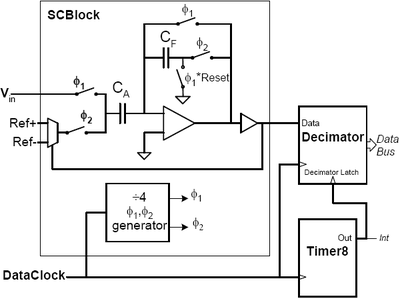

Vstup je integrovaný v jednej fáze časového cyklu a referenčná hodnota je potom integrovaná v opačnom smere druhého cyklu. Referenčný výber, pozitívny alebo negatívny, je riadený komparátorom, a vždy integrovaný späť k nule. Pred integráciou výstupu z komparátora do čítača, je najskôr výsledok komparátora spracovaný decimátorom. Decimátor dvojnásobne integruje vstup na vzorkovaciu frekvenciu. Výstup dvojnásobného integrátora je vzorkovaný pri decimačnej frekvencii (vačšinou 1/64-násobok vzorkovacej frekvencie) a odpočítaný od poslednej výstupnej hodnoty, to udáva diferenciál. Tento diferenciálny proces sa opakuje, stále pri decimačnej frekvencii, z čoho vyplýva nasledujúca prenosová funkcia:

- [math]H(z)=\frac{(1-z^{-M})^2}{(1-z^{-1})^2}[/math]

Použité zdroje

- TUKE FEI-KEMT: A/D a D/A prevodníky na báze Sigma-Delta modulácie

- KUKUČA, Peter, STU BA: Základy číslicového merania

- MOTOROLA: Principles of Sigma-Delta Modulation for Analog-to-Digital Converters

- Cypress Semiconductor Corporation: Analog - ADC Selection - AN2239

- Cypress Semiconductor Corporation: Delta Sigma ADC Data Sheet (DelSig V 1.2)