Prevodníky ADC

| Predmet |

|

|---|---|

| Konfigurovateľné mikroprocesorové systémy | |

| Tématická časť: | |

| Analógové spracovanie signálov |

Obsah

Analógovo-digitálne prevodníky

Analógovo-digitálny prevodník alebo analógovo- číslicový prevodník (ADC z anglického Analog-to-Digital Converter) je elektronické zariadenie na prevod analógového signálu na digitálny signál. Prevod analógového signálu na digitálny je využívaný pomerne často, keďže signály sa skoro výlučne analyzujú a spracovávajú číslicovo. Príkladom konkrétnych aplikácií analógovo-digitálneho prevodu sú elektronické diktafóny, mobilné telefóny, kamery s digitálnym záznamom, automatizované zberače dát v laboratóriách s následným digitálnym vyhodnotením a archiváciou nameraných dát, či plynový pedál v moderných automobiloch, ktorý už nie je spojený lankom s klapkou na prívod vzduchu, ale uhol jeho stlačenia je meraný potenciometrom, ďalej zdigitalizovaný - s následnou vypočítanou akciou klapky prívodu vzduchu, ktorá je ovládaná motorovým aktorom.

Druhy bežne používaných ADC:

- integračný, s dvojnásobnou integráciou - pomalý ale presný, používaný najmä v meracích prístrojoch

- s postupnou aproximáciou (kombinácia digitálno-analógového prevodníka, komparátora a príslušnej logiky) - stred v cene aj rýchlosti aj presnosti

- flash (najrýchlejší, sústava komparátorov a napäťových referencií)

Teória Analógovo-digitálnych prevodníkov

Pri digitalizácii analógovej informácie máme k dispozícii nespočetné množstvo metód. V nasledujúcom texte sú zhrnuté najjednoduchšie alebo naopak zložité, ale osvedčené.

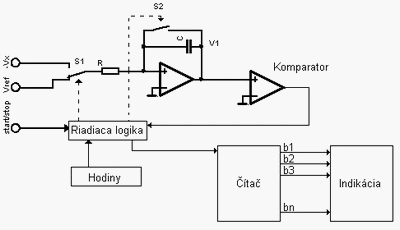

Integračná metóda

Prevodníky postavené na dvojstupňovej integrácii sú najčastejšie využívané v digitálnych meracích prístrojoch. Dôvodom tohto použitia je ich presnosť a odolnosť voči starnutiu prvkov. Ich najchúlostivejšou časťou je integračný článok, ktorý však dnes dokážeme vyrobiť veľmi precízny.

|

| Integračná metóda |

Popis funkcie:

- v dobe T1 ne pripojené Vx, táto doba je konštantná a je daná časom zaplnenia čítača, čiže načítanie 2n inpulzov

- potom sa integrátor pripojí k Vref(má opačnú polaritu ako Vx), nastáva pokles a táto doba končí, keď výstupné napätie prechádza nulou a komparátor dá povel na ukončenie prevodu

- doba T2 je merítkom veľkosti signálu Vx a meria sa počtom impulzov, ktoré čítač načíta v tejto dobe

- na začiatku konverzie je spínač S1 krátko zopnutý a na výstupe integrátoru je nulové napätie, ako náhle sa otvorí na výstupe narastá napätie so strmosťou

[math]\left[\frac{dV_1}{dt}\right]_{behom T_1}=\frac{V_x}{RC}[/math]

- po načítaní 2n impulzov sa čítač nuluje, spínač S1 sa prepne na Vref a na výstupe integrátora bude napätie klesať so strmosťou

[math]\left[\frac{dV_1}{dt}\right]_{behom T_2}=-\frac{V_{ref}}{RC}[/math]

- pritom sa čítajú hodinové impulzy až do nulového napätia na výstupe integrátora, ich počet je daný vzťahom

[math]M=|-V_x|\frac{2^n}{V_{ref}}[/math]

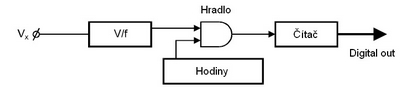

Metóda využitia medziprevodu napätia na frekvenciu

Prevodníky pracujúce na princípe prevodu U na f sa skladajú zo štyroch základných častí:

- prevodník napätia na frekvenciu......jednoduchý napätím preladiteľný oscilátor, obvod s využívajúci integrátor

- generátor hodinového signál

- komparačné AND hradlo

- čítač frekvencie

|

| Metóda využitia medziprevodu napätia na frekvenciu |

Popis funkcie:

- najprv sa prevedie napätie na frekvenciu

- potom sa signál s frekvenciou závislou na vstupnom napätí privedie na porovnávacie AND hradlo

- na druhý vývod tohto hradla sa privedie hodinový signál

- na výstupe sa objaví výsledok, ktorý čítač navzorkuje a podá ďalej

Pozn. pri prevode U na f sa najčastejšie využívajú integrátory, preto by bolo možné zaradiť aj tento ADC medzi integračné;

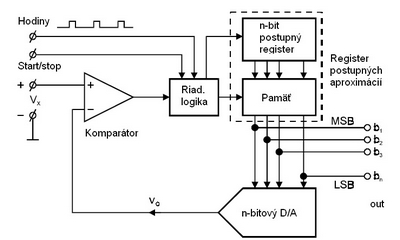

Aproximačná metóda

Aproximačné prevodníky, v literatúre tiež ako kompenzačné alebo prevodníky s postupnou aproximáciou, sú v podstate spätno-väzbové systémy, ktoré autonómne generujú signál a ten následne porovnávajú so vstupným. Pohybujú sa v binárnom strome, odkiaľ čerpajú digitálne kombinácie potrebné kombinácie ako vzory pre generovanie analógového signálu.

|

| Aproximačná metóda |

Popis funkcie:

- na začiatku je register postupných aproximácií vynulovaný

- v prvom kroku je do neho zapísaná 1 ako najvyšší bit a ostatné sú nulové

- vygeneruje sa signál(zodpovedajúci 100...0) a ten sa porovná so vstupným

- podľa výsledku porovnania sa rozhodne o platnosti 1 alebo nahradení 0, ak je vstupný signál nižšej úrovne

- tento proces pokračuje pokiaľ sa nenavzorkuje daný počet bitov

- vzorkovanie sa v podstate stáva pohybom po binárnom strome úrovne rovnej rozlíšeniu aproximácie

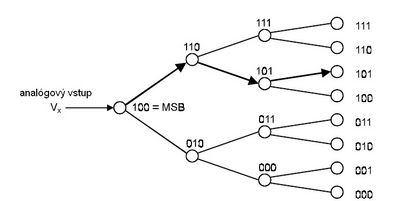

Pozn. pohyb po binárnom strome možností je na nasledujúcom obrázku;

|

| Aproximačná metóda - pohyb po bipolárnom strome |

Pozn. výhoda tohto prevodníku je jeho rýchlosť, pretože na navzorkovanie N bitov potrebuje N hodinových inpulzov, čo je značné zníženie počtu voči integračnému, ktorý ich potreboval 2N

Metóda založená na sledovaní vstupného signálu

Prevodníky založené na tejto technológii sú podobné aproximačným prevodníkom, avšak nepoužívajú zložitú pamäť. Pamäť je nahradená vratným čítačom.

Popis funkcie:

- prevodník sa skladá z troch častí: komparátor, vratný čítač, n-bit DA prevodník

- signál z DA prevodníka a vstup sú privedené na vstup komparátora

- výstup komparátora je pripojený na vratný čítač, ktorý sa podľa neho inkrementuje alebo dekrementuje

- jeho hodnota je výstupom a zároveň opravným signálom, ktorý vstupuje do DA a následne do komparátora

Pozn. jeho rýchlosť je značne obmedzená neschopnosťou vykonať náhle skoky, mnohým aplikáciám však plne vyhovuje, kvôli vyhladenému a spojitému výstupu

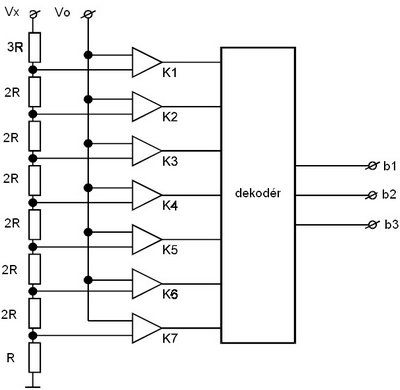

Metóda paralelného vzorkovania

Prevodníky využívajúce túto metódu sú najrýchlejšími prevodníkmi, pretože dokážu navzorkovať celé binárne slovo naraz. Ich funkcia je založená na rozložení úrovne vstupného signálu na rezistorovom rade. Napätie je snímané na každom spoji dvoch rezistorov a je vpodstate opakom paralelného A/D prevodníka. Z toho vyplýva aj jeho najväčšia nevýhoda, čo je konštrukčná zložitosť. Na n-bitov totiž treba 2n-1 komparátorov a 2n rezistorov. Aj napriek tomu sa kvôli svojej rýchlosti často používajú. Pozn. nasledujúci obrázok je hrubá schéma jeho stavby

|

| Metóda paralelného vzorkovania |

ADC prevodníky v PSoC

Poznáme 3 základné druhy ADC prevodníkov implementovaných v PSoC

- Postupná aproximácia registra (SAR - Successive Approximation Register)

- Prídavný

- Delta Sigma

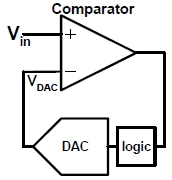

Postupná aproximácia registra (SAR)

SAR je zložený z komparátora a DAC prevodníka, ako je vidieť na obrázku.

|

| SAR ADC Bloková schéma |

Na začiatku prevádzacieho cyklu, je DAC nastavený na polovičnú veľkosť a porovnanie je uskutočnené medzi VIN a výstupom DAC. V každom krokom je DAC aktualizovaný, nasledujúci bit vybratý následne porovnaný s hodnotami DAC pomocou binárneho vyhľadávania. Tento typ prevodníka je rýchly, ale používa 100% PSoC CPU pri konverzii a vyžaduje mať stabilný vstup po celú dobu premeny. Čo sa týka SAR ADC prevodníkov, je to robené len na vzorke a má okruh, ktorý nie je k dispozícii a ešte nie je zahrnutý v PSOC.

Prídavný

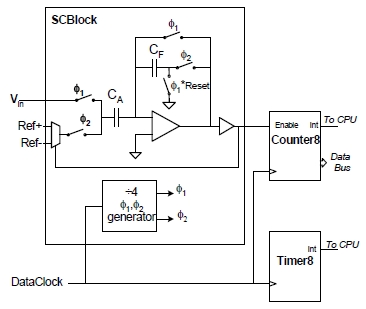

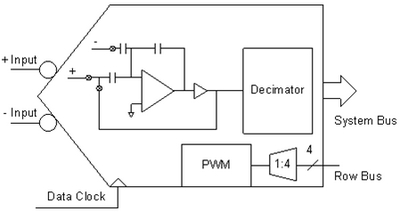

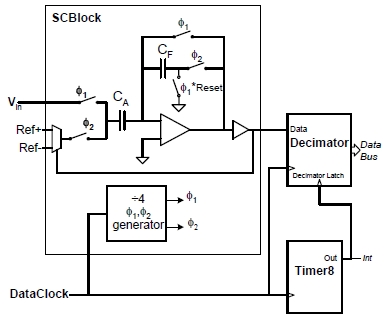

Prídavné prevodníky používajú integrátor, komparátor a pár referencií ako je na obrázku (Prírastkový ADC - Bloková schéma). Vstup je integrovaný v jednej fáze cyklu. 1 pár príslušnej časti je potom integrovaný v opačnom smere v 2. fáze cyklu. Výber príslušnej súčiastky, je pozitívne alebo negatívne riadený komparátorom a vždy integrovaný späť k nule. Počet cyklov, v ktorých je porovnávaný výstup pozitívny sa započítava do digitálneho výsledku. To je algoritmus zodpovedajúci dvojakej stupnici ADC.

|

| Prírastkový ADC - Bloková schéma |

Prírastkový ADC vytvára 2n porovnaní aby vytvorilo n-bitovú konverziu. Prevodník integruje signál počas tvorenia vzorky. Toto má za dôsledok vyčlenenie časového úseku vysokofrekvenčného zvuku. Všetky PSoC prírastkové prevodníky sú taktované 4x na vzorkovaciu frekvenciu; čítač a časovač musia sedieť s rozdeľovačom 4-fázového hodinového generátora v analógovom stĺpci. PSoC prírastkové prevodníky sú dostupné v niekoľkých variantoch:

ADCINC12

ADCINC12 je časovaný na 4-krát vzorkovací kmitočet a potrebuje 14-bitový časovač a 14-bitový sčítavač, aby sa mohla uskutočniť 12-bitová konverzia. Prvé 2 bity oboch – časovač aj sčítač udržujú v rovnováhe rozdeľovač. Dva digitálne bloky vykonávajú nižších 8 bitov časovača a nižších 6 bitov sčítača. Vyšších 6 bitov časovača a sčítača je vykonávaných softvérom na prerušenie činnosti.

ADCINC14

ADCINC14 – používa o 2 časové bloky naviac než ADCIN12. Toto umožňuje aby 16-bitová časová funkcia bola uskutočnená bez softvéru na prerušenie činnosti, s vylúčením možnosti prerušujúcich latentných chýb.

ADCINCVR

ADCINCVR – toto je najflexibilnejší PSoC ADC, ale taktiež vyžaduje najviac kódový priestor pre jednoduchý prevodník. Vzorkovaciu frekvenciu je možné jemne upraviť pomocou parametra CalcTime. Toto dovoľuje integráciu počas celého cyklu periodického rozsahu typicky 50-60Hz

|

| ADCINDVR - Bloková schéma |

ADCINC

ADCINC – používa zosilňovač bežne spojený s Delta Sigma prevodníkmi namiesto sčítavača. Toto zachráni jeden digitálny blok a obmedzuje umiestnenie na jednoduchý prípad. Tento prevodník nie je tak ľahko nastaviteľný so zreteľom na vzorkovací kmitočet.

|

| ADCINC - Bloková schéma |

DualADC

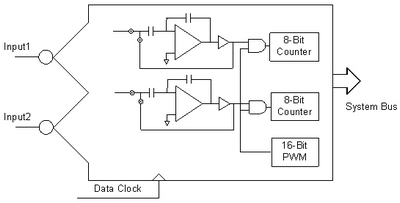

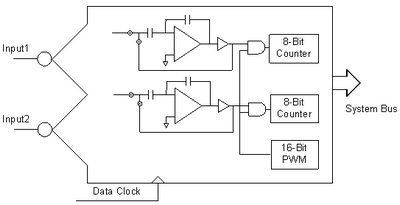

DualADC – Duálny ADC je rozvinutý ADCINCVR. Každý z 2 časovo synchronizovaných prevodníkov používa zvlášť integrátorový/komparátorový blok a zvlášť 8-bitový sčítavať pre nižších 6 bitov výsledku. Preto duálny ADC si vyžaduje o jeden digitálny blok naviac ako ADCINCVR. Vyššie bity prevodu vykonávajú v sčítači softvéru. Veľa z firmware v DualADC API spĺňa bit manipulovanie potrebné pre variabilné riešenie funkcie.

|

| DualADC - Bloková schéma |

DualADC8

DualADC8 je zjednodušený DualADC. Použitím Single-byte prevodníka pre každý z 2 výsledných, šetrí kódový priestor a čas na kalkuláciu v prevode počas prevodu

|

| DualADC8 - Bloková schéma |

TrialADC

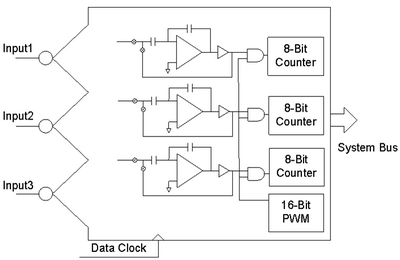

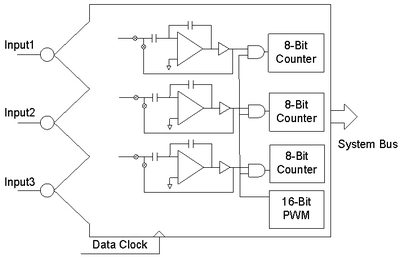

TriADC je rozšírený ADCINCVR. Každý z 3 časovo synchronizovaných prevodníkoch sa používa oddelený integrátorový/komparátorový blok a oddelený 8-bitový odčítač pre nižších 6-bitov výsledku. Preto TriADC vyžaduje o 2 ďalšie digitálne bloky naviac ako ADCINCVR. Vyššie bity prevodu sú vykonávané v softvérovom sčítači. Množstvo z firmware v TriADC API implementuje bity potrebné pre variabilné riešenie funkcie.

|

| TriADC - Bloková schéma |

TrialADC8

TriADC8 - je zjednodušený TriADC. Použitím single-byte prevodníka pre každý z dvoch výsledkov sa šetrí značná časť kódového priestoru a výpočetného času v prevode.

DualADC a TriADC sú obzvlášť užitočné v aplikáciách kde množstvo výsledkov musí byť premieňaných súčasne a multiplexné oneskorenie by malo za následok nepresné výsledky. Príkladom takejto aplikácie je výpočet napájania v PMoCBasic1 Referencie Design.

|

| TriADC8 - Bloková schéma |

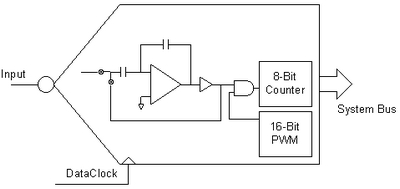

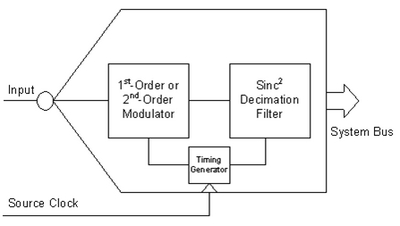

Delta Sigma

Delta sigma ADC využíva tú istú integračnú/porovnávaciu topológiu ako inkrementované meniče. Radšej než integrovať porovnávací výstup v registri, výsledky komparátora sú vypočítavané v zlomku, ako môžete vidieť na obrázku. Zlomok dvojnásobne integruje vstup pri vzorovom pomere. Výstup tohto dvojitého integrovania je vzorkovaný pri zlomkovom pomere(najčastejšie 1/64 násobok vzorového pomeru) a vyňatý s poslednej výstupnej hodnoty, získavajúc diferenciál. Diferenciálny postup je opakovaný stále pri zlomkovom pomere.

Toto je sinc2 filter. Jeho výhodou je inkrementačný menič výstupných dát pri zlomkovom pomere vzorového pomeru namiesto 2n krát vzorkovacieho pomeru. Výstup obsahuje dáta z dvoch predošlých vzorov. Keď vstup Delta Sigmy meniča je združený, dva vzory musia byť premenené aby došlo k odstráneniu starých dát pred potvrdením nových dát. Toto určuje minimálny rozsah pre skenované dáta.

|

| Delta Sigma ADC - Bloková schéma |

V CY8C25/26xxx a CY8C22/24/27xxx, výpočet rozdielu je vyhotovený v programe. CY8C29xxx má vylepšený decimátor, ktorý obsahuje funkciu rozdielu a znižuje výpočtové nároky.

DELSIG8

DELSIG8 používa jednoduchý blok pre funkciu časovača a delí 64. Tento ADC má výstupnú hodnotur 31 ksps pre vzorovú hodnotu 500ksps.

DELSIG11

DELSIG11 používa rovnaké hardwarové nastavenie ako DELSIG8, ale delí 256. Má výstupnú hodnotu 7.8 ksps pre vzorovú hodnotu 500 ksps. Rýchlejšie výstupné hodnoty sú možné pri obetovaní linearity.

DelSig

Menič Delsig poskytuje široký rozsah zlomkových hodnôt s rozličným rozlíšením pre každý z nich. Topológia, ktorá je delená 32 alebo 64 používa jednoduchý digitálny blok, topológie delené 128 či 256 používajú dva bloky. Digitálne bloky používané na časovanie majú taktiež programovateľné PWM. Použitie dvojitého modulátoru vylepšuje SNR a umožňuje zvýšenie rozlíšenia o tri údery pri akomkoľvek zlomkovom rozsahu. Vylepšený delič v CY8C29xxx rodokmeni značne znižuje nároky na CPU pri všetkých premieniacich hodnotách.

|

| DelSig - Bloková schéma |

Zdroje

- http://sk.wikipedia.org/wiki/Anal%C3%B3govo-digit%C3%A1lny_prevodn%C3%ADk

- http://www.cypress.com/?docID=17396

- Cypress PSoC Designer 5.1 - Datasheet