4-bitový binárny čítač: Rozdiel medzi revíziami

Skočit na navigaci

Skočit na vyhledávání

| Riadok 1: | Riadok 1: | ||

__NOTOC__ | __NOTOC__ | ||

[[Category:Simulácie a modelovanie]] | [[Category:Simulácie a modelovanie]] | ||

| + | {{Simulacia_modelovanie_3|4}} | ||

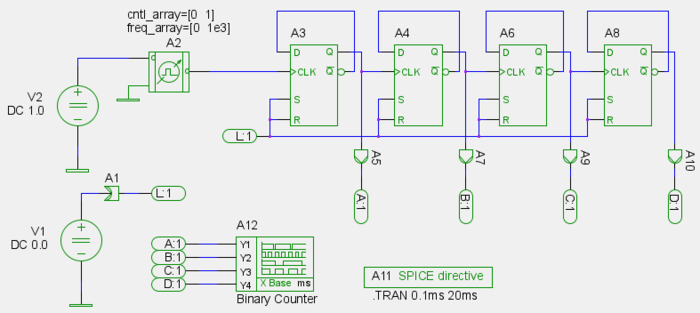

Pre simuláciu 4 bitové binárneho count-down čitača bol použitý generický [[D_dff | D klopný obvod ]]. Zdrojom hodinového signálu je ''analógovým'' napätím riadený ''digitálny'' [[ D_osc | generátor ]] '''A2'''. | Pre simuláciu 4 bitové binárneho count-down čitača bol použitý generický [[D_dff | D klopný obvod ]]. Zdrojom hodinového signálu je ''analógovým'' napätím riadený ''digitálny'' [[ D_osc | generátor ]] '''A2'''. | ||

Aktuálna revízia z 22:55, 22. marec 2013

Pre simuláciu 4 bitové binárneho count-down čitača bol použitý generický D klopný obvod . Zdrojom hodinového signálu je analógovým napätím riadený digitálny generátor A2.

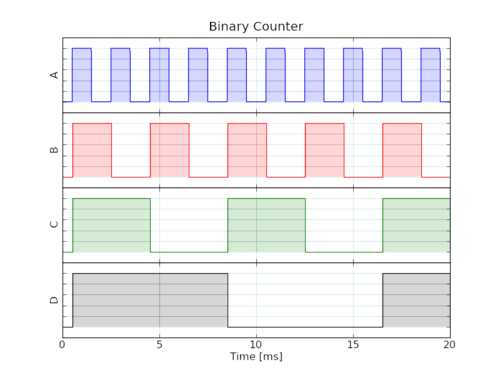

V simulácii bol na zobrazenie 4 signálov s logickými úrovńami použitý komponent PLOT_Y4D

Úlohy

- Upravte obvod tak, aby bola na výstupoch A-D vzostupná (count-up) postupnosť.