Synchrónna komunikácia SPI

| Predmet |

|

|---|---|

| Konfigurovateľné mikroprocesorové systémy | |

| Tématická časť: | |

| Sériové komunikačné zbernice |

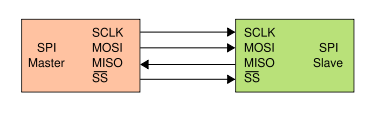

SPI (Serial Peripheral Interface) je štvorvodičová synchrónna sériová zbernica pracujúca v móde full duplex slúžiaca na prepojenie periférií s mikropočítačmi. Protokol bol definovaný firmou Motorola v produktovej línii mikroradičov MC68HCxx. Zariadenia komunikujú spôsobom master/slave, kde zariadenie master iniciuje dátový rámec. Použitie SPI v prípadoch, kedy je k jednému zariadeniu master pripojených viacero zariadení slave, je síce možné, ale na ich realizáciu musí master disponovať potrebným počtom slave select (chip select) vývodov (pri bežnom zapojení). SPI sa niekedy nazýva "four wire" sériová zbernica ako opak ku three, two a one wire sériovým zberniciam.

Obsah

Rozhranie zbernice SPI

Zbernica SPI špecifikuje štyri logické signály:

- SCLK - Serial Clock (výstup od zariadenia master)

- MOSI/SIMO - Master Output, Slave Input (výstup od zar. master)

- MISO/SOMI - Master Input, Slave Output (výstup od zar. slave)

- SS - Slave Select (active low - logickú jednotku reprezentuje nižšia úroveň napätia; výstup od zar. master)

Alternatívne pomenovania, ktoré sú tiež často používané:

- SCK, CLK - Serial Clock

- SDI, DI, SI - Serial Data In, Data In, Serial In

- SDO, DO, SO - Serial Data Out, Data Out, Serial Out

- nCS, CS, CSB, nSS, STE - Chip Select, Slave Transmit Enable

Pri pomenovaní SDI/SDO (DI/DO, SI/SO) je vyžadované, aby SDO na zariadení master bolo spojené s SDI na slave a naopak. Polarita Chip Select je zriedkakedy active high (logickú jednotku reprezentuje vyššia úroveň napätia), aj keď niektoré značenia (SS alebo CS namiesto nSS, nCS) naznačujú opak.

Činnosť zbernice SPI

Zbernica SPI vie pracovať s jedným zariadením master a jedným alebo viacerými zariadeniami slave. Ak sa používa iba jedno zariadenie slave, SS pin môže byť zafixovaný na nižšiu úroveň napätia, ak to zariadenie dovoľuje. Niektoré zariadenia vyžadujú na pine SS hranu prechodu napätia z vyššej úrovne na nižšiu pre iniciáciu akcie, napríklad AD prevodník Maxim MAX1242. Ak je pripojených viacero zariadení slave, je potrebný samostatný SS signál zo zariadenia master do každého zariadenia slave. Väčšina zariadení slave má trojstavový výstup, takže ich signál MISO sa stane hi-Z (vysoko-impedančný, "odpojený" - neovplyvňuje obvod, do ktorého je zapojený), keď zariadenie nie je vybraté. Zariadenia bez trojstavového výstupu nemôžu zdielať segmenty SPI zbernice s ostatnými zariadeniami. Iba jedno takéto zariadenie môže komunikovať so zariadením master a iba jeho SS môže byť aktivované.

Prenos dát

Pred začatím komunikácie master najskôr nastaví hodinový signál SCLK na hodnotu frekvencie menšej alebo rovnej maximálnej frekvencie, ktorú slave podporuje. Tieto frekvencie sú väčšinou v rozsahu 1-70 MHz. Master potom vyberie požadovaný slave nastavením jeho signálu SS na úroveň logickej jednotky. Ak je nutná čakacia doba (napríklad pri AD prevode), potom master musí čakať minimálne po tento čas, kým začne vykonávať hodinové cykly. Počas každého hodinového cyklu SPI sa vykoná fulll duplexový prenos dát:

- master pošle bit po linke MOSI, slave ho z tejto linky prečíta

- slave pošle bit po linke MISO, master ho z tejto linky prečíta

Nie všetky prenosy vyžadujú všetky štyri operácie, ale vykonajú sa, aj keď nemajú význam. Pri prenosoch sa väčšinou používajú dva posuvné registre veľkosti danej dĺžkou slova, napríklad osem bitov, jeden v zariadení master, druhý v zariadení slave. Sú spojené do kruhu. Dáta sa väčšinou vyberajú od najsignifikantnejšieho bitu a do rovnakého registra sa presunie nový najmenej signifikantný bit. Po tom, čo je tento register vybratý, si master a slave navzájom vymenili hodnoty v registroch. Následne každé zariadenie vezme túto hodnotu a nejak ju spracuje, napríklad si ju zapíše do pamäte. Ak existujú ďalšie dáta, ktoré majú byť vymenené, posuvné registre sa naplnia novými hodnotami a proces sa opakuje. Prenos môže trvať ľubovoľný počet hodinových cyklov. Keď už nie sú žiadne dáta, ktoré majú byť prenesené, master prestane vysielať hodinový signál. Väčšinou potom odznačí slave. Prenos sa často skladá z osembitových slov. Bežné sú však aj iné dĺžky slov, napríklad 16-bitové pre touchscreeny alebo audio kodeky (TSC2101 od Texas Instruments) alebo 12-bitové pre mnohé DA a AD prevodníky. Každý slave na zbernici, ktorý nebol aktivovaný cez SS linku, musí ignorovať vstupujúci hodinový a MOSI signál a nesmie vysielať cez MISO. Master musí vybrať v danom čase iba jeden slave.

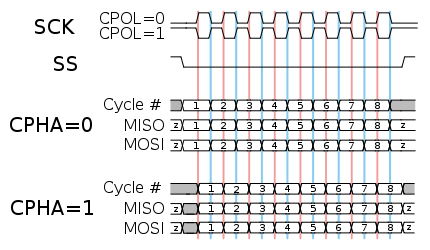

Polarita a fáza hodinového signálu

Okrem frekvencie hodinového signálu musí master nastaviť aj jeho polaritu a fázu vzhľadom na prenášané dáta. Príručka SPI Block Guide od Freescale Semiconductor nazýva tieto dve možnosti CPOL a CPHA a väčšina predajcov toto pomenovanie používa.

Opis časového diagramu zobrazeného na obrázku (platí pre zariadenie master aj slave):

- Pri CPOL=0 je základná hodnota hodinového signálu nula

- Pri CPHA=0 sú dáta čítané pri nábežnej hrane signálu (prechod 0 -> 1) a menia sa pri dobežnej hrane (prechod 1 -> 0)

- Pri CPHA=1 sú dáta čítané pri dobežnej hrane signálu a menia sa na nábežnej hrane

- Pri CPOL=1 je základná hodnota hodinového signálu jedna (inverzne k CPOL=0)

- Pri CPHA=0 sú dáta čítané pri dobežnej hrane signálu a menia sa pri nábežnej hrane

- Pri CPHA=1 sú dáta čítané pri nábežnej hrane signálu a menia sa pri dobežnej hrane

Takže CPHA=0 znamená vzorkovanie na úvodnej hrane hodinového signálu a CPHA=1 znamená vzorkovanie na koncovej (druhej) hrane signálu, pričom nezáleží na tom, či je hrana nábežná alebo dobežná. Všimnite si, že pri CPHA=0 musia byť dáta stabilné polovicu cyklu pred prvým cyklom hodinového signálu. Pri všetkých módoch CPOL a CPHA musí byť počiatočná hodnota hodinového signálu nastavená pred zvolením zariadenia slave. Tiež si všimnite, že "dáta sú prečítané" v tomto dokumente zvyčajne znamená "dáta môžu byť prečítané". Signály MOSI a MISO sú zvyčajne stabilné (v bode ich prijatia) polovicu cyklu až do ďalšieho prenosu hodinového signálu. Zariadenia master a slave na SPI zbernici môžu vzorkovať dáta v iných bodoch tejto polovice cyklu. To dáva komunikačnému kanálu medzi zariadeniami väčšiu možnosť flexibility. Niektoré produkty používajú inú konvenciu názvov. Napríklad TI MSP430 používa namiesto CPOL názov UCCKPL a UCCKPH namiesto CPHA. Pri spájaní dvoch čipov dajte pozor na inicializačné hodnoty fázy hodinového signálu.

Čísla módov

Kombinácie hodnôt polarity a fázy sa často označujú ako módy, ktoré sú bežne očíslované podľa pravidla, že CPOL označuje vyšší bit čísla a CPHA nižší bit.

| Mód | CPOL | CPHA |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

Ďalším bežne používaným spôsobom reprezentácie módu je usporiadaná dvojica (CPOL,CPHA), napríklad hodnota "(0,1)" by znamenala CPOL=0 a CPHA=1.

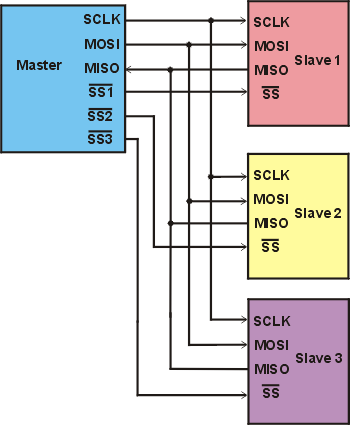

Konfigurácia SPI s nezávislými zariadeniami slave

V konfigurácií s nezávislými zariadeniami slave existuje samostatná linka SS pre každé zo zariadení. Toto je bežný spôsob použitia zbernice SPI. Keďže sú MISO piny zariadení slave spojené, musia to byť trojstavové piny.

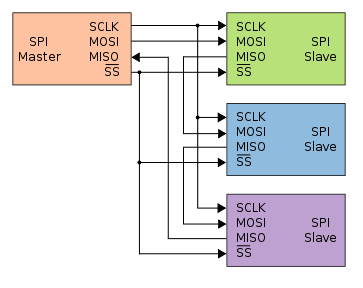

Konfigurácia SPI daisy reťaz

Niektoré produkty so zbernicou SPI sú navrhnuté tak, aby bolo možné zapojiť ich v konfigurácií daisy reťaz - výstup prvého zariadenia slave je spojený so vstupom druhého atď. Porty všetkých zariadení sú navrhnuté tak, aby počas druhej skupiny impulzov hodinového signálu posielali presnú kópiu toho, čo prijali počas prvej skupiny impulzov. Celá reťaz sa chová ako posuvný register používaný pri SPI. Daisy reťazenie je často robené pomocou posuvných registrov, aby poskytli zásobník pre vstupy a výstupy zo zbernice. Toto zapojenie potrebuje iba jednu linku SS zo zariadenia master.

Správnosť komunikácie

SPI nepodporuje komunikačný protokol zabezpečujúci potvrdenie prijatia dát zariadením slave. Niektoré zariadenia slave sú navrhnuté tak, aby ignorovali komunikáciu, v ktorej je počet impulzov hodinového signálu vyšší, než je špecifikované. Iným zariadeniam tento stav nevadí, ignorujú vstupy, ktoré sú navyše a posúvajú rovnaký výstupný bit. Pre rôzne zariadenia je bežné používanie SPI komunikácie rôznej dĺžky, napríklad pri testovaní digitálneho integrovaného obvodu, kedy sa vyšle príkazové slovo jednej dĺžky (napr. 32 bitov) a dostane sa odpoveď inej dĺžky (napr. 153 bitov).

Prerušenia

Zariadenia pripojené na zbernicu SPI niekedy používajú ďalšiu linku na posielanie signálu prerušenia do hostiteľského CPU, napríklad prerušenie od udalosti dotyku obrazovky pri senzoroch touchsreenu, prekročenia limitnej teploty pri snímačoch teploty, alarmy vygenerované čipmi s hodinami reálneho času atď. Štandard SPI nezahŕňa prerušenia, ich použitie nie je ani zakázané, ani špecifikované.

Softvérová implementácia protokolu

Príklad softvérovej implementácie protokolu SPI pre zariadenie master s CPOL=0, CPHA=0 a dĺžkou slova osem bitov v programovacom jazyku C. Keďže CPOL=0, napätie hodinového signálu musí byť nastavený na nižšiu úroveň predtým, než je zvolené zariadenie slave. Pred začatím prenosu musí byť aktivovaná linka SS daného zariadenia slave a po jeho skončení zase deaktivovaná. Väčšina periférií povoľuje alebo vyžaduje viacero prenosov kým je linka SS aktívna. Táto rutina môže byť pred zrušením vybratia čipu volaná viackrát.

unsigned char SPIBitBang8BitsMode0(unsigned char byte)

{

unsigned bit;

for (bit = 0; bit < 8; bit++) {

/* zápis MOSI pri koncovej hrane predchádzajúceho hodinového signálu */

if (byte & 0x80)

SETMOSI();

else

CLRMOSI();

byte <<= 1;

/* polovica cyklu hodinového signálu pred začiatočnou/nábežnou hranou */

SPIDELAY(SPISPEED/2);

SETCLK();

/* polovica cyklu hodinového signálu pred koncovou/dobežnou hranou */

SPIDELAY(SPISPEED/2);

/* čítanie MISO pri koncovej hrane */

byte |= READMISO();

CLRCLK();

}

return byte;

}

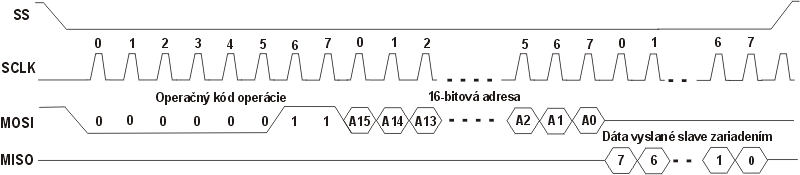

Príklad priebehu kominukácie

Okrem klasickej komunikácie s prenosom kontinuálneho dátového toku ako je to napríklad v prípade AD prevodníka, umožňuje SPI pripojenie zariadení s možnosťou adresácie ako sú pamäte. Spôsob adresovania spočíva vo vyslaní operačného kódu operácie, ktorá sa bude vykonávať, slave zariadeniu bezprostredne po jeho výbere (aktivácii) signálom SS. Na základe tohto kódu je nastavený režim operácie slave zariadenia. Následne je možné vyslať napríklad 16-bitovú adresu ak je to v prípade adresovania EEPROM pamäte uvedeného na nasledujúcom obrázku. Bezprostredne po zaadresovaní nasleduje vysielanie dát slave zariadením.

Klady a zápory SPI

Klady

- Komunikácia full duplex

- Vyššia priepustnosť než pri I2C alebo SMBus

- Flexibilita prenosu bitov

- Nie je obmedzená na osembitové slovo

- Ľubovoľný výber veľkosti správy, obsahu a účelu

- Extrémne jednoduché hardvérové rozhranie

- Používa oveľa menej káblov než paralelné rozhrania

- Nanajvýš jeden signál pre každé zariadenie zvlášť (SS), ostatné sú zdieľané všetkými zariadeniami

- Signály sú jednosmerné, čo umožňuje galvanickú izoláciu

Zápory

- Potrebuje viac pinov na integrované obvody než I2C aj pri variante "3-Wire"

- Žiadna hardvérová kontrola toku (ale master môže oddialiť ďalšiu hranu hodinového signálu aby spomalil prenosovú rýchlosť)

- Žiadne hardvérové potvrdenie od zariadenia slave (master by nemusel "hovoriť s nikým" bez toho, aby si to všimol)

- Podporuje iba jedno zariadenie master

- Nie je definovaný protokol kontroly chýb

- Vo všeobecnosti náchylná na chyby spôsobené šumom

- Bez formálneho štandardu nie je možná kontrola zhody

- V porovnaní s RS-232, RS-485 alebo CAN zvláda iba malé vzdialenosti

Použitie

SPI sa používa na komunikáciu s viacerými periférnymi zariadeniami, napríklad:

- Snímače teploty, tlaku, dotykové obrazovky, AD prevodníky

- Riadiace zariadenia: audio kodeky, digitálne potenciometre, DA prevodníky

- Šošovky fotoaparátov, kamier

- Komunikačné zariadenia: Ethernet, USB, USART, CAN, IEEE 802.15.4, IEEE 802.11

- Pamäte: flash a EEPROM

- Hodiny reálneho času

- LCD displeje

- MMC a SD karty

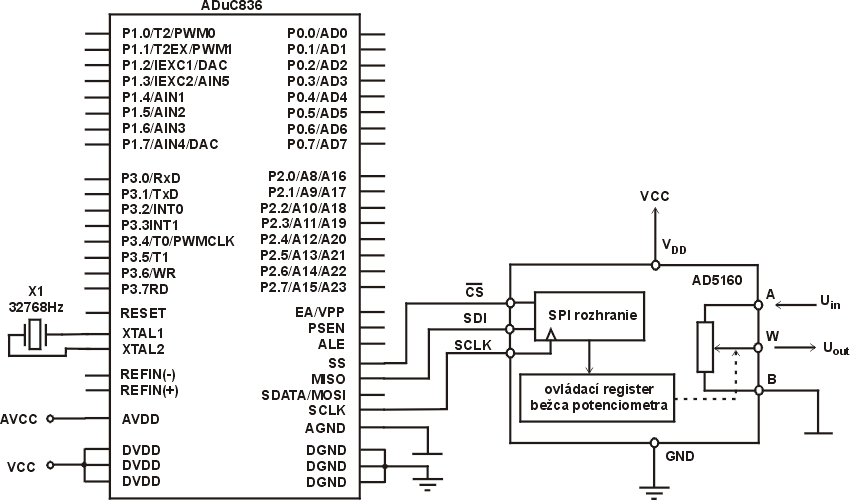

Príklad aplikácie SPI

Pomocou SPI rozhrania je k mikropočítaču ADuC836 pripojený digitálny potenciometer AD5160. Vstupné napätie Uin na vývode A je regulovateľné v celkovom počte 256 rôznych pozícií. Vyslaním príslušných dát sa riadi register bežca potenciometra. Na vývode W je potom možné odoberať regulované napätie Uout. Týmto spôsobom je možná náhrada mechanického potenciometra v aplikáciách s potrebou regulácie napätia ako je napríklad regulácia hlasitosti pri zosilňovačoch alebo regulácia referenčného napätia pre stabilizovaný zdroj a iné.

Štandardy

Zbernica SPI je skôr upravovaná podľa potrieb jej používateľov než prijatá medzinárodnou komisiou. Nedostatočná štandardizácia sa prejavila vo veľkom výbere možností protokolu. Rozdielne dĺžky slov sú bežné. Každé zariadenie definuje svoj vlastný protokol vrátane toho, či vôbec podporuje príkazy. Niektoré zariadenia sú iba vysielače, iné sú iba prijímače. Signál voľby zariadenia slave je niekedy active-high, inokedy active-low. Niektoré protokoly posielajú ako prvý najmenej signifikantný bit. Niektoré zariadenia majú dokonca ďalšie rozdiely v módoch okrem CPOL/CPHA, ktoré boli opísané vyššie. Posielanie dát od zariadenia master k zariadeniu slave môže byť vykonané počas opačnej hrany než posielanie od slave ku master. Zariadenia často potrebujú prídavný čas nečinnosti pred prvým alebo posledným hodinovým signálom, alebo medzi príkazom a odpoveďou naň. Niektoré zariadenia vyžadujú prídavný signál kontroly toku od slave k master, ktorý indikuje, kedy sú dáta pripravené. To vedie k päťvodičovému protokolu namiesto zvyčajného štvorvodičového. Takýto signál "pripravený" alebo "povolený" je často active-low a musí byť povolený pri kľúčových udalostiach, napríklad po príkazoch alebo medzi slovami. Bez tohto signálu by musela byť značne obmedzená rýchlosť toku alebo by v protokole museli byť vložené bezvýznamové bajty, ktoré by vyhovovali najhoršiemu možnému prípadu času odpovede zariadenia slave. Medzi príklady patrí inicializácia AD prevodu, adresovanie správnej stránky flash pamäte. Mnoho zariadení master nepodporuje priamo tento signál, ale spolieha sa na fixné oneskorenie. Mnoho SPI čipov podporuje iba správy, ktorých dĺžka je násobkom 8 bitov. Takéto čipy nemôžu spolupracovať s protokolmi JTAG alebo SGPIO ani so žiadnymi inými, ktoré potrebujú správy inej dĺžky, než je násobok 8 bitov. Dokonca existujú rozdieli na úrovni hardvéru. Niektoré čipy majú skombinované MOSI a MISO v jednej linke (SI/SO). Toto sa niekedy nazýva trojvodičová (3-Wire) signalizácia. Na iných čipoch nie sú linky na výber zariadenia (SS), výber sa deje iným spôsobom. Avšak toto sa väčšinou neoznačuje ako 3-Wire. Ak niekto potrebuje externý konektor pre SPI, definuje si svoj vlastný. Úrovne signálov záležia len na čipe.