Architektúra mikrokontroléra

Jednočinný počítač alebo ang. Microcontroller (Mikrokontrolér, MCU) je väčšinou monolitický integrovaný obvod dosahujúci kompletní mikropočítač. Jednočinné počítače sa vyznačujú veľkouspoľahlivosťou a kompaktnosťou, preto sú určené predovšetkým pre jednoúčelové aplikácie ako je riadenie, regulácia a pod. Často sú jedno čipové počítače súčasťou vstavaných (embedded) systémov.

|

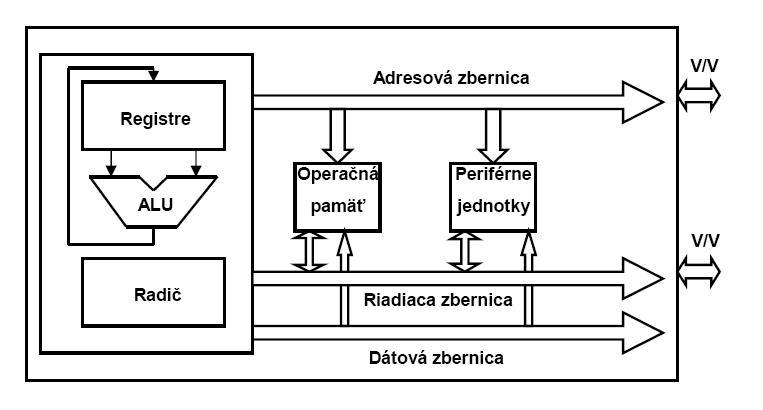

| Štruktúra mikrokontroleru |

Jednočipový mikropočítač - Mikrokontroler vznikne, ak sa mikroprocesor doplní o periférne obvody (pamäte, obvody vstupu/výstupu a iné rozhrania) a spolu sú umiestnené do jedného puzdra. Jednočipový mikropočítač disponuje určitou univerzálnosťou a možnosťou modifikovať jeho funkciu na základe programu, prípadne rozšírením o ďalšie periférne obvody.

|

| Mikrokontroler |

Mikrokontrolery vo všeobecnosti obsahujú:

- Radič a aritmetickú jednotku. Podľa typu mikrokontroleru sa používa dĺžka slova 4,8,16 alebo

32 bitov

- Pamäť programu (kódovú pamäť). Pamäť programu je buď typu EPROM alebo Flash, u mikrokontrolerov

vyrábaných pre určitú konkrétnu aplikáciu s pevne daným programom je typu ROM

- Pamäť typu R/W, niekedy doplnená pamäťou EPPROM

- Periférne obvody pre vstup a výstup dát

Architektúra

Jednočipový počítač je integrovaný obvod, ktorý v sebe zahrňuje spravidla všetko potrebné k tomu, aby mohol dosiahnuť celú aplikáciu, bez toho, aby potreboval ďalšie podporné obvody.

Existujú základné dve architektúry mikroprocesorov – von Neumannova a Harvardská, každá má svoje výhody i nevýhody. Pri súčasnom stupni integrácie sa zrejme častejšie využíva Harvardská architektúra,vysoký stupeň integrácie dovoľuje pripojiť rôzne bloky pamäte pomocou vlastných zberníc. Delenie na „Harvardskou“ a „Von Neumannova“ architektúru je však pri dnešnom stupni integrácie už len akademické. U moderných architektúr sa často užívateľovi adresný priestor javí navonok ako lineárny (Von Neumannovský),zatiaľ čo fyzicky sú pamäte k jadru pripojené pomocou niekoľko nezávislých zberníc (napr. jedna zbernica pre FLASH/ROM (pamäť programu),druhá pre užívateľskú vnútornú RAM a zásobník, tretia pre pripojenie integrovaných pamäťovo mapovaných periférií, ďalšia pre pripojenie externou RAM).

Von Neumannova architektúra

Von Neumannova architektúra je architektúra, pre ktorú je typická spoločná pamäť pre dáta i program. Toto usporiadanie má výhody v tom, že nepotrebujeme rozlišovať inštrukcie pre prístup k pamäti dát a pamäti programu, čo vedie k zjednodušeniu vlastného čipu. Ďalšou výhodou je, že je potreba iba jednej dátovej zbernice, po ktorej sa prenášajú oba typy dát, čo je výhodné v prípade použitia externých pamätí, kde sa redukuje potrebný počet nutných vstupov a výstupov. Nevýhodou je, že prenos oboch typov dát po jednej zbernici je pomalší, ako pri oddelených zberniciach pre pamäti dát a programu.

Harvardská architektúra

Harvardská architektúra je typická oddelením pamäti programu a pamäti dát. Hlavnou nevýhodou tejto architektúry je väčšia technologická náročnosť daná nutnosťou vytvoriť dve zbernice. Za hlavnú výhodu je možné považovať možnosť inej šírky programové a dátové zbernice. Tejto možnosti sa široko využíva, takže nájdeme osembitové mikrokontrolery s programovou zbernicou širokou 12, 14 i 16 bitov. Medzi ďalšie výhody harvardskej architektúry patrí rýchlosť vykonávania inštrukcií, pretože inštrukcie i potrebné dáta je možné čítať v jedom čase.

Architektúra mikrokontrolera rady 8051

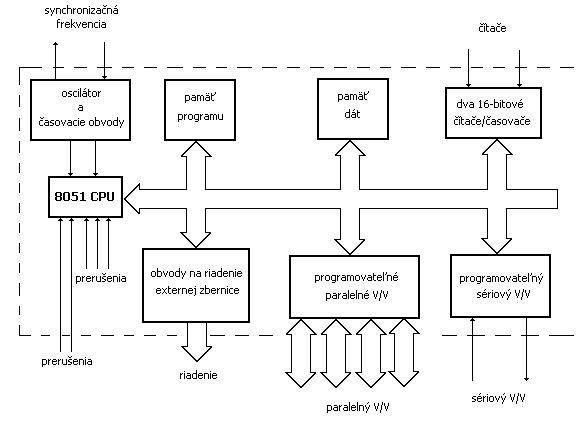

|

| Architektúra mikrokontrolerov rady 8051 |

Inštrukčné súbory

V oblasti jednočipových počítačov sa bežne používajú inštrukčné súbory typu CISC, RISC a DSP

|

| Čítač inštrukcií |

CISC

- označuje procesor so „zložitým inštrukčným súborom“. Procesor podporuje mnoho formátov a druhú inštrukciu. Na jednu stranu to znamená úsporu miesta v programovej pamäti (vyššiu hustotu kódu), na druhej strane to však znamená komplikovanejší dekodér inštrukcií vo vlastnom mikrokontroléri a pomalšie spracovanie inštrukcií

RISC

- RISC označuje procesor s redukovaným inštrukčným súborom. Základnou myšlienkou je obmedzenie počtu a zjednodušení kódovaní inštrukcií, čo vedie ku zjednodušeniu inštrukčného dekodéra. Hlavnou výhodou tohto prístupu je rýchlosť a jednoduchosť, na rovnakej ploche čipu môže byť miesto 16bitového procesoru CISC 32bitový procesor RISC. Nevýhodou je, že pre zakódovanie inštrukcie je potrebné viac miesta, niekedy musíme použiť dve inštrukcie miesto jednej, takže klesá hustota kódu.

DSP

- Digitálny signálový procesor alebo tiež digitálny signálny procesor (skratka DSP) je mikroprocesor, ktorého návrh je optimalizovaný pre algoritmy používané pri spracovaní digitálne reprezentovaných signálov. Hlavným nárokom na systém býva priebežné spracovanie veľkého množstvá dát „pretekajúcich“ procesorom.

Mikrokontrolery 8051 sa vyrábajú v širokom sortimente výkonov a veľkostí. Najmenšie typy majú len 8 vývodov vrátane napájania a rozmery puzdra 3x3 mm, najvýkonnejšie typy majú puzdrá so 100-200 vývodmi.

Mikrokontrolery 8051 obsahujú vo všeobecnosti:

- pamäťový podsystém

- centrálnu procesorovú jednotku

- obvody časovania

- blok čítačov/časovačov

- sériový programovateľný V/V obvod

- paralelný programovateľný V/V obvod

- obvodovy na riadenie externej zbernice

- prerušovací systém

- interná 8-bitová zbernica na prenos dát a inštrukcií

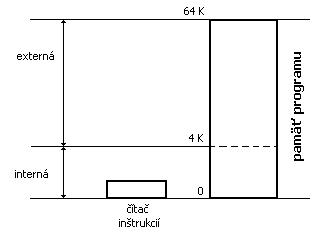

Pamäťový systém mikrokontrolerov 8051

Delenie pamäťového podsystému

Pamäťový systém delíme na:

- pamäť programu – 4KB, možnosť rozšírenia na 64 KB

- pamäť dát – 128 Bytov (256 Bytov) + 64 Bytov

Pamäť programu delíme na:

- internú - umiestnenú na čipe, kapacita 4 kB (rozsah adries 0000H – 0FFFH)

- externú – kapacita 60 kB (rozsah adries 1000H – FFFFH)

Adresný priestor pamäti programu sa adresuje 16-bitovým čítačom inštrukcií (PC register).

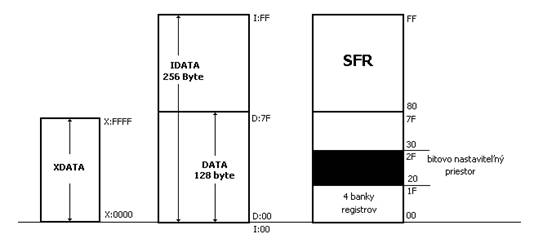

Pamäť dát mikrokontrolera 8051

|

| Pamäť dát |

Delenie pamäti dát

- Internú (kapacita 256 bytov)

- typ RWM (128 bytov)

- skupina SFR (Special function register 128 bytov)

- Externú – rozšírenie internej pamäti o 64 bytov

Interná pamäť dát typu RWM obsahuje:

- 4 banky 8-bitových registrov označených RB0 až RB3. Každá banka obsahuje 8 registrov R0 až R7. Banky registrov sú umiestnené na adresách 00H až 1FH. Spolu je v bankách 32 8 – bitových registrov.

- bitovo adresovateľnú pamäť RWM na adresách 20H až 2FH.V tejto oblasti môžeme adresovať každý bit samostatne. Rozsah bitových adries je od 00H až po 7FH.

- oblasť pamäti pre univerzálne použitie v rozsahu adries 30H – 7FH.

Skupina SFR obsahuje:

- špeciálne funkčné registre

- bitovo adresovateťné pamäťové miesta pre:

- akumulátor ACC

- register B

- programové stavové slovo PSW

Mikrokontrolery rady AVR

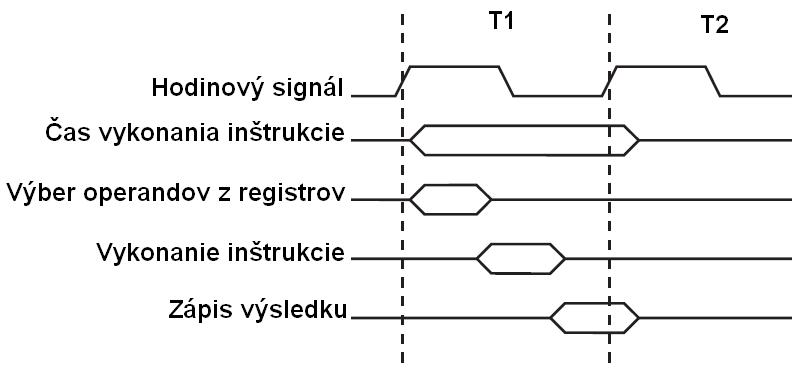

Označenie AVR je priradené mikrokontrolérom spoločnosti Atmel s RISC architektúrou (Reduced instruction set – Redukovanou inštrukčnou sadou), vyvinutých na mieru predovšetkým pre nízkoúrovňový programovací jazyk C. Oproti klasickým mikroprocesorom 8051 naznali sa dočkali rady základnych zmien. Ide predovšekým o zvätšenie šírky inštrukčného slova na 16 bitov. Čo umožnilo zrýchlenie načítavania inštrukcií, kde až na niekoľko výnimiek dochádza k načítaniu v priebehu jedného strojového cyklu. Dalším pokrokom tejto rady je priame propojenie ALU (aritmeticko logickej jednotky) s 32 pracovnými registrami, čo viedlo k zníženiu počtu hodinových taktov potrebných k vykonaniu väčšiny inštrukcií iba na dva takty (načítanie + dekódovanie a vykonanie). Vďaka tomu, že instrukcia vystačí s jedným slovom, bolo možné využiť jednoduchého prekrývania inštrukcí (pipelining). Toto prekrývanie spôsobuje, že v okamžiku dekódovania a vykonávania jednej inštrukcie dochádza k súčastnému nahrávaniu nasledujúcej inštrukcie. Počet hodinových taktov potrebných na vykonanie inštrukcie typu register-register sa tým znížil na jeden hodinový takt.

|

| Časovanie jednocyklovej aritmeticko-logickej inštrukcie |

Pri krátkom porovnaní s jadrom 8051 je vidieť, že AVR poskytuje až 12x vyšší výpočtový výkon pri rovnakom hodinovom kmitočte. Pretože jeden strojový cyklus mikroprocesora odpovedá jednej perióde oscilátora, pri 8051 je jeden strojový cyklus rovný dvanástim periódam oscilátora.

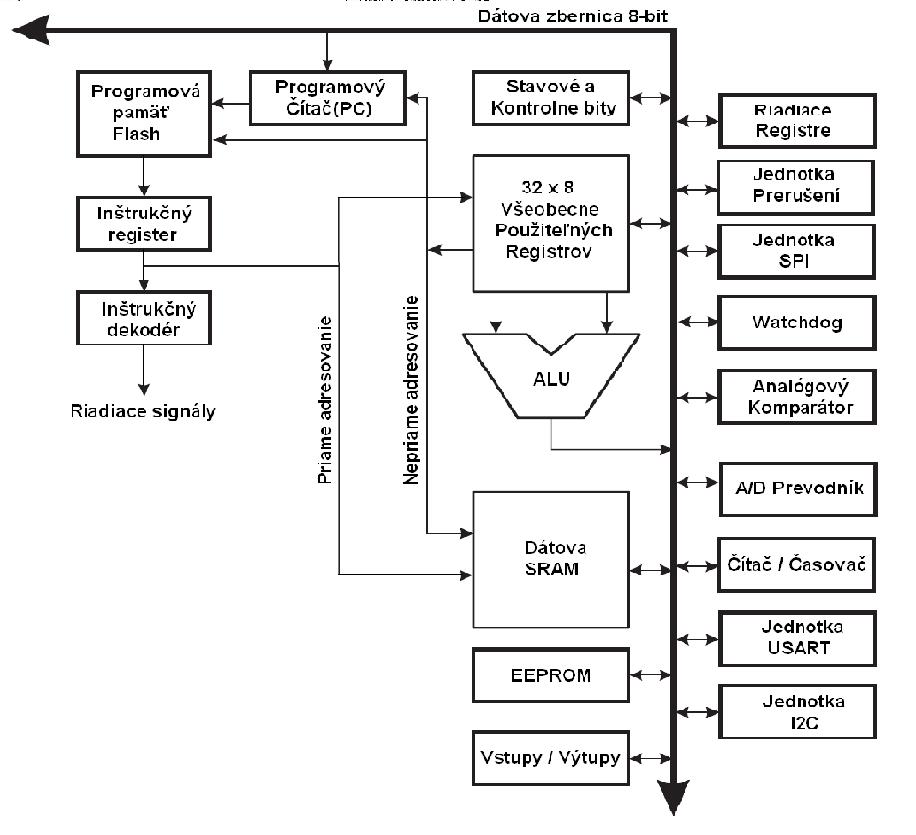

Architektúra mikrokontrolera rady AVR

Mikrokontroléry AVR sú Harvardského typu (oddelená pamäť pre program a dáta). Na čipe sú však implementované tri typy pamätí. Pamäť typu Flash má šírku 16 bitov a je využitá pre uloženie programu. Pamäť SRAM má šírku 8 bitov a je využívana pre ukladanie dát. Nakoniec pamäť EEPROM slúži pre odkladanie dát, ktoré je potreba zachovať i pri odpojení napájacieho napätia. Prístup do EEPROM sa zaisťuje nastavením príslušných registrov a komunikácia s ňou je pomalšia.

|

| Všeobecná architektúra mikrokontrolerov rady AVR |

LITERATÚRA

- http://home.zcu.cz/~dudacek/Pot/mikrokontrolery.pdf

- [stargate.cnl.tuke.sk/~klimek/SKOLA/JM/otazky_1-2.doc]

- http://robotika.yweb.sk/skola/!elektronika%20modelu%20automatickeho%20skladu/popis.doc