Komunikačné rozhranie I2C

Architektúra ARM mikrokotnrolérov

Obsah

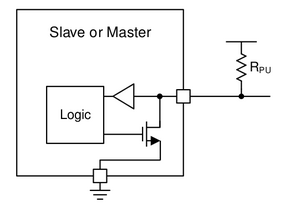

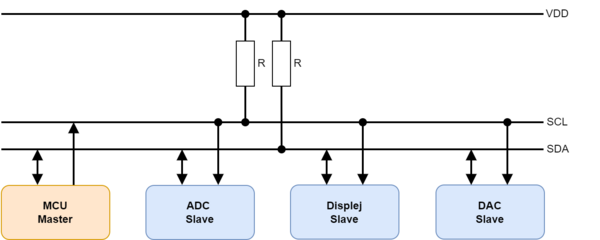

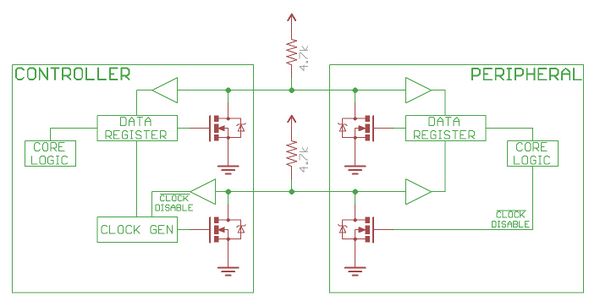

Inter-Integrated Circuit alebo I²C je dvojvodičová obojsmerná zbernica vyvinutá firmou Philips začiatkom 90-tych rokov 20. storočia, používaná predovšetkým na prepojenie periférnych zariadení s mikrokontrolérom. Na zbernicu sú pripojené zariadenia rozdelené na riadiace (Master - zahajuje a ukončuje komunikáciu; generuje hodinový signál SCL) a riadené (Slave - zariadenie adresované Masterom) [1] na Obr. 1 [2]

|

|

Obr. 1 A)Pripojenie zaradení na zbernicu, B) Interná schéma zapojenia rozhrania I2C[3]

SDA (Serial Data) je dátový signál a SCL (Serial Clock) je hodinový signál. Hodinový signál je vždy generovaný aktuálnym radičom zbernice; niektoré periférne zariadenia môžu niekedy vynútiť nízku hodnotu hodinového signálu, aby radič oneskoril odoslanie ďalších údajov (alebo aby potreboval viac času na prípravu údajov pred pokusom radiča o ich taktovanie). Tento postup sa nazýva "natiahnutie hodín" (clock stretching).

Terminologická poznámka: Označenie master/slave môže byť nahradené označním controller/peripheral.

I2C umožňuje prepojenie až 128 rôznych zariadení s pomocou iba dvoch obojsmerných vodičov. Jeden tvoria hodinový signál SCL (Synchronous Clock) a druhý dátový kanál SDA (Synchronous Data). Maximálna dĺžka vodičov je daná ich najvyššou povolenou kapacitou 400 pF, všeobecne sa uvádza cca 10cm. Každý vodič musí byť pripojený jedným pull-up rezistorom ku kladnému napätiu, čo zaistí vysokú úroveň v pokojovom stave. Pri prebiehajúcom prenose sú na SDA vysielané jednotlivé dátové bity pričom platí pravidlo, že logická úroveň na SDA sa môže nastaviť len ak je SCL v úrovni L. Toto pravidlo je porušené v dvoch špeciálnych prípadoch, a to pri vysielaní podmienok START a STOP, ktoré sa používajú na začatie komunikácie a k ukončeniu prenosu. Maximálna frekvencia signálu SCL je podľa verzie I2C 100 kHz alebo 400 kHz. Pre obe frekvencie je daná minimálna povolená doba zotrvania SCL v úrovni L a H. Pri komunikácii aj pri prenose dát si jednotlivé stanice synchronizujú generátory hodín tak, že trvanie úrovne H na SCL je odmeriavané vnútorným časovačom každej stanice až od okamihu, keď SCL skutočne úrovne H dosiahne (pretože je SCL typu otvorený kolektor, môže byť v úrovni L držaný aj v situácii kedy sa daná stanica snaží nastaviť úroveň H). Podobne je doba trvania úrovne L na SCL odmeriavaná od zostupnej hrany. Tento mechanizmus umožňuje pre niektoré zo staníc spomaliť prenos: pomalá stanica môže podržať po určitú dobu signál SCL v úrovni L a tým zabrániť vysielajúcej stanici vo vyslaní ďalšieho bitu. Zbernica I2C neumožňuje duplexný prenos, v jednom okamihu vysiela len jedno zariadenie. Všetky zariadenia pripojené na zbernicu musia mať individuálnu adresu a implementovaný mechanizmus komunikácie pomocou I²C zbernice [1][2].

Princíp obojsmernej komunikácie[4]

Otvorený kolektor označuje typ výstupu, ktorý môže stiahnuť napäťovú úroveň zbernica na nízku úroveň - teda log.0 (vo väčšine prípadov na zem), alebo "uvoľniť" zbernicu a nechať napätie aby pomocou pull-up rezistora stúplo na úroveň logicej.1. V prípade, že je zbernica uvoľnená uzlom master alebo slave, pripojený pull-up rezistor je zodpovedný za vytiahnutie zbernice na úroveň napájacieho napätia. Keďže žiadne zariadenie nesmie vynucovať vysokú úroveň napätie na linke (teda úroveň pre log.1), znamená to že na zbernici nikdy nedôjde ku komunikačnému problému, keď sa jedno zariadenie pokúsi pripojiť napätie pre úroveň log.1 a iné zariadenie stiahne zbernicu na úroveň log.0, čo by spôsobilo skrat (napájacie napätie na zem). I2C vyžaduje, aby v prípade že master v zapojení s viacerými mastermi vysiela a vidí, že linka je v úrovni log.0 (iné zariadenie ju ťahá nadol - teda iné zariadenie komunikuje), zastaví komunikáciu, pretože zbernicu používa iné zariadenie.

Obr. 1x. Základná štruktúra linky SDA/SCL

Obr. 1x zobrazuje zjednodušenú schému vnútornej štruktúry master alebo slave zariadenia pre komunikačné linky SDA/SCL. Táto schéma obsahuje vyrovnávaciu pamät (buffer) na čítanie vstupných údajov a znižujúci (pull-down) tranzistor FET na prenos údajov. Zariadenie je schopné meniť napäťovú úroveň iba na log.0 (vytvoriť skrat na zem) alebo uvoľniť linku zbernice (vysoká impedancia voči zemi) a umožniť, aby pull-up rezistor zvýšil napätie. Toto je dôležitý koncept, ktorý si treba uvedomiť pri práci s I2C zariadeniami, pretože žiadne zariadenie nesmie zvyšovať úroveň napätia pre log.1. Táto vlastnosť umožňuje obojsmernú komunikáciu medzi uzlami master a slave.

Protokol prenášaných údajov[2]

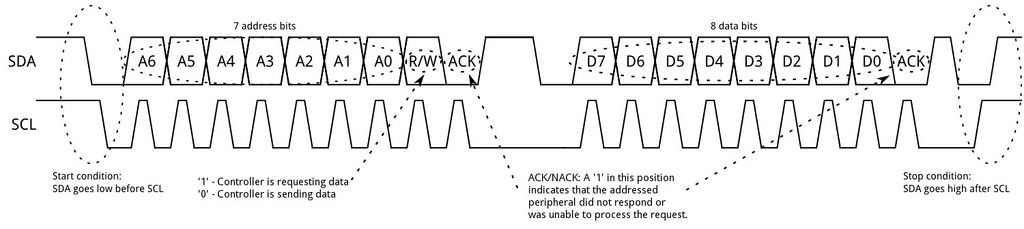

Údaje v rozhraní I2C sa prenášajú v tzv. správach. Každá správa je rozdelená do jednotlivých rámcov, a to: adresný rámec, ktorý identifikuje binárnu adresu Slave zariadenia a následne jeden alebo viacero dátových rámcov, ktoré obsahujú prenášaný obsah. Správy obsahujú aj bity pre čítanie/zápis, bity ACK/NACK a podmienky START a STOP (Obr. 2).

Obr. 2. Štruktúra správy cez I2C rozhranie[3]

- START - podmienka štart signalizuje začiatok komunikácie. Linka SDA sa prepne z vysokej (log. 1) na nízku hodnotu (log. 0) skôr, ako sa linka SCL prepne z vysokej na nízku hodnotu.

- ADDRESS - adresa Slave zariadenia, s ktorým chce Master komunikovať. Adresa predstavuje 7 alebo 10 bitové celé číslo v binárnom tvare, ktoré predstavuje jedinečný identifikátor každého Slave zariadenia. Dve zariadenia by nemali mať tú istú adresu v jednej I2C zbernici.

- RW - jeden bit, ktorý určuje či sa vykonáva operácia zápisu alebo čítania:

- Ak RW = 0, zápis údajov na Slave zariadenie.

- Ak RW = 1, čítanie údajov zo Slave zariadenia.

- ACK/NACK nasleduje za každým rámcom v správe. Je to bit potvrdenia/nepotvrdenia:

- Ak bol úspešne prijatý adresný alebo dátový rámec, prijímajúce zariadenie vráti odosielateľovi log. 0 (ACK - Acknowledged).

- Ak nastala chyba v prenose, prijímajúce zariadenie vráti odosielateľovi log. 1 (NACK - Not Acknowledged).

- Existuje niekoľko situácií, ktoré vedú k vytvoreniu NACK:

- Prijímač vykonáva nejakú funkciu v reálnom čase a nie je pripravený začať komunikáciu s Masterom.

- Prijímač odbrží neznáme údaje alebo príkazy.

- Počas prenosu prijímač nemôže prijímať ďalšie dátové bajty.

- Master ukončí čítanie údajov a oznámi to Slave zariadeniu pomocou NACK.

- DATA - Dátový rámec je vždy dlhý 8 bitov a posiela sa s najvýznamnejším bitom (MSB) ako prvým. Za každým dátovým rámcom bezprostredne nasleduje bit ACK/NACK na overenie, či bol rámec úspešne prijatý. Pred odoslaním ďalšieho dátového rámca musí bit ACK prijať buď master, alebo slave (v závislosti od toho, kto dáta odosiela).

- STOP - ukončovacia podmienka štart signalizuje koniec komunikácie. Linka SDA sa prepne z nízkej (log. 0) na vysokú hodnotu (log. 1) potom, čo sa linka SCL prepne z nízkej úrovne na vysokú [5][6].

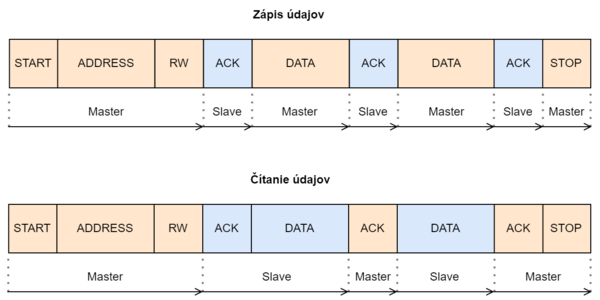

Obr. 3. Časový priebeh zápisu a čítania údajov v I2C rozhraní

Dátový prenos na zbernici I2C[7]

- Master vyšle štart podmienku každému pripojenému slave prepnutím linky SDA z úrovne vysokého napätia na úroveň nízkeho napätia pred prepnutím linky SCL z vysokej na nízku.

- Master posiela každému uzlu slave 7 alebo 10-bitovú adresu s ktorým chce komunikovať, spolu s bitom pre čítanie/zápis

- Každý slave porovnáva adresu odoslanú od mastera so svojou vlastnou adresou. Ak sa adresa zhoduje, podriadená jednotka vráti bit ACK tým, že potiahne linku SDA na jeden bit. Ak sa adresa od nadradeného zariadenia nezhoduje s vlastnou adresou podriadeného zariadenia, podriadené zariadenie ponechá linku SDA na úrovni log.1.

- Master odošle alebo prijme dátový rámec

- Po prenose každého dátového rámca prijímacie zariadenie vráti odosielateľovi ďalší bit ACK, aby potvrdilo úspešné prijatie rámca

- Ak chcete zastaviť prenos dát, master pošle podriadenému zariadeniu stop podmienku prepnutím SCL na vysokú hodnotu pred prepnutím SDA na vysokú hodnotu.

Na Obr.3 je vyobrazený časový diagram zápisu a čítania údajov s veľkosťou 2B prostredníctvom rozhrania I2C.

Základné vlastnosti a parametre zbernice I2C

Základná pracovná frekvencia linky je 100kHz. Špecifikácia I2C dovoľuje zvýšiť túto frekvenciu až na 3.4 MHz. Zvýšenie frekvencie na strane mikrokontroléra je záležitosť konfigurácie. Je potrebné zvoliť takú frekvenciu, ktorú podporuje pripojený senzor alebo zariadenie, s ktorým chceme komunikovať.

| Časovanie | SCL |

|---|---|

| Standard Mode | 100 kHz |

| Fast Mode | 400 kHz |

| Fast Mode Plus | 1 MHz |

| High Speed Mode | 3.4 MHz |

Zdroje a odkazy

- ↑ 1,0 1,1 Gabriel Gašpar a Juraj Ďuďák. Využitie mikrokontrolérov v automatizovanom riadení. Spektrum, 2023. ISBN: 978-80-227-5283-1.

- ↑ 2,0 2,1 2,2 Matúš Nečas: Multi-displej systém pre embedded aplikácie, Bakalárska práca, MTF STUBA, 2023

- ↑ 3,0 3,1 https://learn.sparkfun.com/tutorials/i2c/all

- ↑ Texas Instruments, Understanding the I2C Bus, Application Report SLVA704 - June 2015. https://www.ti.com/lit/slva704

- ↑ Scott Campbell. BASICS OF THE I2C COMMUNICATION PROTOCOL. https://www.circuitbasics.com/basics-of-the-i2c-communication-protocol/.

- ↑ Sal Afzal. I2C Primer: What is I2C? (Part 1). https://www.analog.com/en/technical-articles/i2c-primer-what-is-i2c-part-1.html.

- ↑ https://www.circuitbasics.com/basics-of-the-i2c-communication-protocol/