A/D Prevodník typu Delta-Sigma: Rozdiel medzi revíziami

| Riadok 77: | Riadok 77: | ||

Tieto vlastnosti sigma-delta prevodníkov sú prakticky opakom nevýhodných vlastností konvenčných prevodníkov, čo im zabezpečuje široké možnosti využitia. Základnou nevýhodou sigma-delta prevodnikov je ich relatívne nízka vstupná frekvencia vzorkovania, čo obmedzuje ich využitie v systémoch ČSS s maximálnou frekvenciou vzorkovania rádovo 100ky KHz. | Tieto vlastnosti sigma-delta prevodníkov sú prakticky opakom nevýhodných vlastností konvenčných prevodníkov, čo im zabezpečuje široké možnosti využitia. Základnou nevýhodou sigma-delta prevodnikov je ich relatívne nízka vstupná frekvencia vzorkovania, čo obmedzuje ich využitie v systémoch ČSS s maximálnou frekvenciou vzorkovania rádovo 100ky KHz. | ||

| + | |||

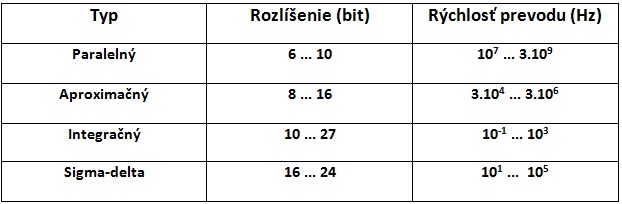

[[Súbor:rrrr.jpg|center|thumb|700px|Obr. 5 Parametre A\D prevodníkov ]] | [[Súbor:rrrr.jpg|center|thumb|700px|Obr. 5 Parametre A\D prevodníkov ]] | ||

Verzia zo dňa a času 17:34, 23. jún 2010

A/D prevodník zaisťuje prevod vstupného analógového signálu na výstupny číslicovy signál.Vstupným signálom býva najčastejšie napätie, výstupom potom dátove slovo o stanovenom počte bitov. Prevod spojitého analógového signálu na diskrétny číslicovy tvar sa u väčšiny prevodníkov uskutočňuje v dvoch krokoch. Analógovy sa najskôr periodicky vzorkuje, t.j. získava sa postupnosť uzkych impulzov, pričom ich amplitúdy odpovedajú analógovemu signálu v príslušnych časových okamžikoch.V druhom kroku sú amplitúdy jednotlivých signálov prevádzane tzv. kvantovaním na číslicovy tvar.Kvantizácia priraduje jednotlivým vzorkám diskrétnu hodnotu (výstupné dátove slovo).

Presnosť prevodu nieje teoreticky obmedzená, ale musíme dodržať nasledujúce zásady:

-Vzorkovanie analógoveho signálu je spracované aspoň s dvojnásobným opakovacím kmitočtom ako je najvyššia harmonická zložka snímaného analógoveho napätia (Nyquistuv teorém)

-Vzorkovacie impulzy su dostatočne úzke

-Kvantovanie vzorkovacích impulzov je dostatočne "jemné",číslo vyjadrujúce amplitúdu ma dotatočny počet rádov, teda výstupné dátove slovo má dostatočný počet bitov

Uvedené procesy majú svoje technické možnosti. Rýchlosť zmeny analógového signálu, ktorú je možné zachytit a digitalizovať, má svoje medze v rýchlosti a rozlišovacej schopnosti kvantovacieho obvodu A/D prevodníku.

Rýchlosť vzorkovania

Rýchlosť vzorkovania vstupného signálu patrí medzi najvýznamnejšie parametre A/D prevodníkov. Musí byť dostatočne vysoká vzhľadom k najvyššej zložke vstupného analógového napätia. Pokial nás naopak niektorá vyššia harmonická zložka nezaujíma alebo spôsobuje chybu v následnom spracovaní dát (napr. šumový signál),je možné ju odstrániť vhodnou dolnou priepusťou.

Rýchlosť prevodu

Je u A\D prevodníkov obvykle rovnaká s rýchlosťou vzorkovania, resp. naopak, rýchlosť vzorkovania vyplýva z najkratšej možnej doby prevodu. Doba prevodu môže byť určená ako doba, ktorá uplynie od okamžiku privedenia vstupného analógového napätia na vstup prevodníku, až do doby, kedy je výstupu prevodníku k dispozícii platné výstupné dátove slovo. Môže byť vyjadrená počtom úplnych prevodov za jednotku času alebo počtom bitov za jednotku času.

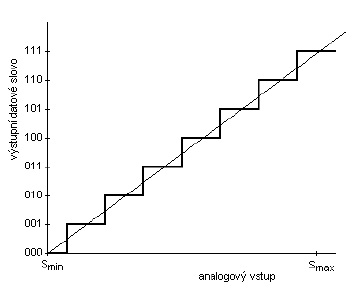

Rozlišovacia schopnosť sa súčasne rovná kvantizačnému kroku Q.Chybu vzniknutú kvantovaním nazývame kvantizačná chyba. Môže dosahovať maximálne hodnoty rovné polovici hodnoty zmeny napätia, ktorá by vyvolala zmenu výstupného dátoveho slova o jeden bit najnižšieho rádu (LSB). Maximálna chyba prevodu je tak u ideálneho prevodníku. Na Obr. 1 je znázornená ideálna prevodová charakteristika A\D prevodníku. Zmeny prevodovej charakteristiky od ideálneho tvaru sú ďalším zdrojom chýb. Schodovitý priebeh prevodovej charakteristiky spôsobuje odchýlku od ideálneho priebehu a prejavuje sa ako kvantizačný šum SNR (Signal-to-Noise Ratio).

Prevodníky typu Delta-Sigma sú moderné prevodníky, vyznačujúce sa jednoduchým hardvérom a zložitým softvérom pracujúcim ako signálovy procesor.Obsahujú integrátor,komparátor a číslicový filter. Vyrábajú sa 16-24 bitové. Na vstupe A/D prevodníka býva často multiplexor, ktorý umožňuje súčasne sledovať niekolko analógových veličín. Čím sú ich zmeny pomalšie, tím viac veličín môžeme sledovať jedným prevodníkom. To prináša značné úspory nákladov. Prevodníky sú riadené riadiacími signálmy, po ukončení prevodu generujú niekedy signál potvrdzujúci platnosť vstupných dát. V súvislosti s používaním mikroprocesorov sa stále častejšie dáva prednosť sériovemu vstupu dát pred paralelným.

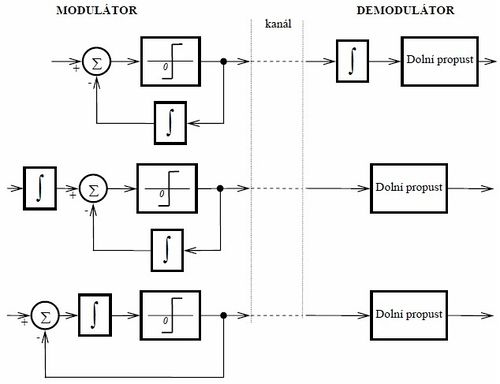

Delta-sigma modulátory sú elektronické obvody, ktoré prevádzajú vstupní analógovy/digitálny signál na diskrétny/analógovy signál na výstupe. Svojim princípom vychádza z delta modulácie. Delta modulovaný signál prenáša informácie o zmene vstupného napätia, pre rekonštrukciu signálu je potom potrebné tento signál invertovať. V delta-sigma modulátore je integrácia (formou sčítania) predradená reťazci. Pretože sa pracuje s diskretizáciou signálu, je nutné dodržať vzorkovací teorém, teda vzorkovací kmitočet musí byť viac než dvakrát väčší než najvyššia frekvencia v signále obsiahnutá. To v delta a delta-sigma modulácii určite splnené bude,signál je vždy výrazne prevzorkovaný.

Delta-sigma modulácia

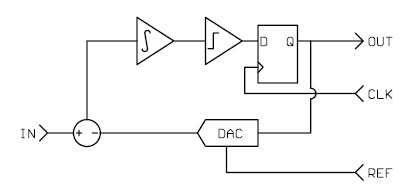

Bloková schéma delta-sigma modulátora je na Obr. 3. Modulátor sa skladá zo sumátora (od vstupného signálu odčíta signál spätnoväzobný),integrátoru (napätie na jeho výstupe rastie či klesá rýchlosťou úmernou výstupu sumátoru), komparátoru (s digitálnym vstupom, napr. "H" pre vstup kladný a "L" pre vstup záporny),pamäti (pri vzostupnej hrane hodinového signálu prenese vstupnú úroveň na výstup a drží až do ďalšej vzostupnej hrany)a v spätnej väzbe je zaradený D/A prevodník. Celé zapojenie je systém so zavedenou zápornou spätnou väzbou.

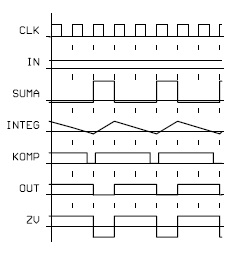

Pre vysvetlenie funkcie sú na Obr. 4 naznačené priebehy napätí za jednotlivými blokmy.V zjednodušenom priklade je uvažovaný konštantný vstupný signál.Pre pochopenie je výhodné začať rozbor od stredu. V obvode sú dve miesta so zapamätaním stavu-integrátor a pamäťová bunka. Hlavne u integrátoru je potrebné poznať východzí stav. Uvažujme teda výstup integrátoru INTEG v kladnej hodnote. Výstup naväzujúceho komparátoru KOMP je "H" a pri príchode prvej vzostupnej hrany je prenesená na výstup OUT, zároveň je vstupom pre digitálne/analógovy prevodník pričom jeho výstup ZV je +VREF

Táto hodnot sa v sumátore odčíta od vstupného napätia IN a ako SUM tvorí vstup integrátora. SUM je po prvej vzostupnej hrane hodín malý záporny signál, teda INTEG pomaly klesá. Pri príchode druhej vzostupnej hrany hodín je výstup integrátora stále kladný, teda na OUT sa opäť zapíše "H" a dej pokračuje. V ďalšom intervale prejde výstup integrátora do zápornej hodnoty, čo rešpektuje komparátor a KOMP prejde do "L", nič viac sa nezmení až do príchodu hodinového impulzu. Jeho vzostupná hrana prenese "L" na výstup OUT a tím DA prevodník (DAC) zmení hodnotu ZV na -VREF. V tomto okamžiku sa zmení aj súčet SUM, ktorý je potom kladný a väčší ako predtým. Výstup integrátoru porastie, porastie omnoho rychlejšie než predtím klesal,vzápätí prejde opäť do kladnej hodnoty, čo sa opäť prejavý na komparátore a celý dej sa v tejto slučke neustále opakuje.

Aby slučka ZV zostala uzavretá musí byť vstupné napätie v intervale (-VREF, +VREF).Rýchlosť nárastu/poklesu napätia na výstupe integrátora je úmerná (proporcionálna) velikosti a polarite vstupného napätia. Preto sa delta-sigma modulácia niekedy nazýva pulzne-proporcionálna.

Funkcia prevodníku z hladiska hardvéru

Pracujú na princípe vyrovnávania náboja so vzorkovanou spätnou väzbou, ktorá udržuje nulovú strednú hodnotu náboja na výstupe integrátora. Hardváre sigma delta prevodníku je veľmi jednoduchý. Je tvorený sigma delta modulátorom a číslicovým filtrom. Sigma delta modulátor prevádza vstupné napätieU1 na pilovitý priebeh, ktorý je komparovaný v komparátore NK a vzorkovaný signálom o kmitočtefs. Vzorkovací kmitočet je podstatne vyšší ako určuje teorém. Následný decimační číslicový filter robí filtráciu typu dolná priepusť a prevzorkovanie kmitočtomfs/K (K= 20-1000).

Vstupné napätie u1 je sčítané s výstupom jednobitového D/A prevodníka,ktorý je v spätnej väzbe.Integrátor potom po taktu pridá vstup sumačného člena k hodnote napätia,ktoré bola na výstupe v predchádzajúcom integračnom takte. Komparátor dá na výstup log.1, ak je vstupné napätie menšie alebo rovné nule,v opačnom prípade dá log.0.Jednobitová spätná väzba sa snaží udržať výstup integrátora na nule tak,že priemerný výstupný tok jednotiek a núl komparátora je úmerný vstupnému napäťiu. Stredná hodnota na výstupe jednobitového prevodníka je rovná vstupnému meranému napätiu.

Výsledkom je bitový tok 1 a 0 pričom jeho stredná hodnota odpovedá vstupnému napätiu.Výstup môže byť čítaní čítačom a následne digitálne filtrovaný.Filter pracuje na decimačnom princípe a koeficient decimácie K je rádovo v stovkách.

Výhody sigma-delta prevodníkov

-Kompatibilita s technológiou VLSI (90% obvodov prevodníka je realizovaných číslicovou technikou), čo umožňuje integráciu týchto prevodníkov spolu s obvodmi DSP na jednom čipe

-Nízka cena týchto prevodníkov vychádza predovšetkým z predchádzajúcej vlastnosti, prispieva k nej aj skutočnosť, že zvyšná časť analógových obvodov nevyžaduje vysokú presnosť(nie sú nevyhnutné presné obvody ani laserové trimrovanie).

-Vysoká linearita je garantovaná princípom činnosti

-Podstatne nižšie nároky na vstupný (obmedzovací) a výstupný (rekonštrukčný) analógový filter, ktoré sú zvyčajne súčasťou kompletného systému ČSS.

Tieto vlastnosti sigma-delta prevodníkov sú prakticky opakom nevýhodných vlastností konvenčných prevodníkov, čo im zabezpečuje široké možnosti využitia. Základnou nevýhodou sigma-delta prevodnikov je ich relatívne nízka vstupná frekvencia vzorkovania, čo obmedzuje ich využitie v systémoch ČSS s maximálnou frekvenciou vzorkovania rádovo 100ky KHz.

Odkazy

[1] [2] [3]