Prevodová charakteristika CMOS invertoru: Rozdiel medzi revíziami

Skočit na navigaci

Skočit na vyhledávání

| Riadok 6: | Riadok 6: | ||

| align="center" | [[Súbor:0040_cmos.png ]] | | align="center" | [[Súbor:0040_cmos.png ]] | ||

|- | |- | ||

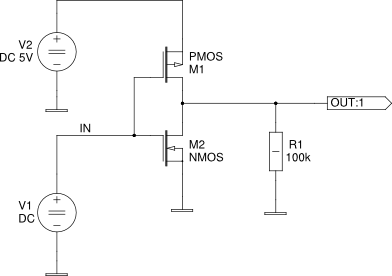

| − | | align="center" width=500 | '''Zapojenie obvodu<ref>http://193.87.70.141/~pf/wiki_upload/sch/ | + | | align="center" width=500 | '''Zapojenie obvodu<ref>http://193.87.70.141/~pf/wiki_upload/sch/0040_cmos_inv.sch</ref><ref>http://193.87.70.141/~pf/wiki_upload/pdf/0040_cmos_inv.pdf</ref>''' |

|} | |} | ||

</center> | </center> | ||

Verzia zo dňa a času 22:46, 30. marec 2010

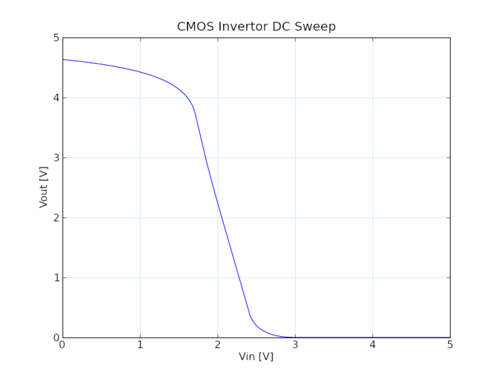

Príklad ukazuje jednosmernú DC analýzu CMOS[1] invertoru. Prevodová charakteristika je definovaná ako závislosť výstupného napätia obvodu Vout od vstupného napätia Vin. Pri výpočte prevodovej charakteristiky meníme hodnota V1 v intervale <0V...5V>. Tranzistory M1 a M2 sú generické MOS tranzistory nmos a pmos simulátora SPICE.

|

| Zapojenie obvodu[2][3] |

V simulácii bol na zobrazenie prevodovej charakteristiky použitý komponent plot_xy.

|

| Výsledok simulácie |

Úlohy

- Z grafu prevodovej charakteristiky určite hranice logických úrovní H a L. Porovnajte hodnoty s výsledkami simulácie TTL invertoru.