Prehľad architektúry PSoC: Rozdiel medzi revíziami

| Riadok 63: | Riadok 63: | ||

=== Digitálne bloky === | === Digitálne bloky === | ||

| − | Digitálne bloky | + | Digitálne bloky <ref>http://www.lubino.sk/rs/3/files/diplomka_-_ubo.pdf</ref> redukujú potrebu použitia ďalších externých obvodov pre požadovanú funkcionalitu pripravovaného zariadenia. Sú určené na spracovávanie a generovanie hlavne digitálneho signálu. Dajú sa programovať a variovať tak, aby poskytovali funkčnosť štandardných elektronických integrovaných obvodov ako napríklad počítadlo, šírkový generátor pulzov, RS-232, IrDA, SPI, I2C príjem a binárnych dát, generátory pseudonáhodných čísel a iné. Taktiež sa používajú na prípravu požadovaného taktovacieho signálu pre analógové bloky, prípadne na spracovanie signálov z analógových blokov (možné prepojenie cez vstupno-výstupné piny). Ich činnosť je nezávislá na behu programu mikroprocesora, avšak môže byť moderovaná programom pomocou API funkcií. |

| − | + | ||

| + | Každý digitálny blok má priradených niekoľko registrov, ktorými sa nastavuje vnútorné zapojenie jeho obvodov a prepojenia s globálnou zbernicou. Tieto registre je možné meniť aj počas práce (za behu) mikroprocesora pomocou programu, a tým aj meniť funkčnosť a zapojenie blokov. Podrobná dokumentácia registrom je rozsiahla a voľne dostupná. Pre prácu s mikroprocesorom, kde za behu programu nedochádza k zmene štruktúry, nie je nutné registre detailne poznať, pretože o ich nastavenie sa postará grafický dizajnér, v ktorom sú už pred pripravené konfigurácie blokov na použitie pre niektoré základné zapojenia a funkcionality. Každé takéto zapojenie spotrebuje jeden alebo viac z blokov mikroprocesora. | ||

| + | |||

| + | Globálne vstupy a výstupy dodávajú digitálnym blokom možnosti na prepájanie taktovacích a dátových vstupov. Podobne ako digitálne bloky, aj globálne | ||

| + | vstupy a výstupy sa nastavujú pomocou k nim prislúchajúceho registra. Podľa konfigurácie registra, jednotlivé bloky pripoja na 8 bitovú, globálnu, vstupnú zbernicu alebo 8 bitovú, globálnu, výstupnú zbernicu. K týmto zberniciam je možné pripojiť i vstupno-výstupné vývody mikroprocesoru. | ||

| + | |||

<references/> | <references/> | ||

Verzia zo dňa a času 19:46, 22. jún 2010

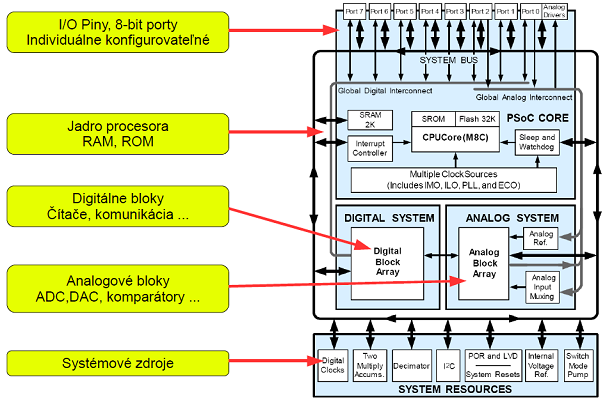

Mikroprocesory PSoC [1] (Programmable System on Chip – Programovateľný systém na čipe) sa skladajú z konfigurovateľných blokov analógových obvodov a digitálnej logiky, ktoré sú vzájomne programovo prepojené. Uvedená architektúra umožňuje vytvárať zákaznícke konfigurácie mikroprocesora tak, aby boli splnené požiadavky potrebné na realizáciu jednotlivých aplikácií. Bloková schéma na Obr. 1.1 zobrazuje architektúru celej rodiny mikroprocesorov PSoC.

Obsah

Vnútorná štruktúra PSoC

Spoločnosť Cypress vyvinula niekoľko desiatok typov súčiastok typov PSoC. Líšia sa predovšetkým množstvom a druhom blokov, veľkosťou pamäti programu (FLASH), pamäťou dát (RAM), veľkosťou a druhom puzdier a ďalšími parametrami. V závislosti na type obsahujú 4-16 digitálnych a 3-12 analógových blokov.

|

| Obr. 1.1 Vnútorná štruktúra PSoC |

M8C – procesorové jadro

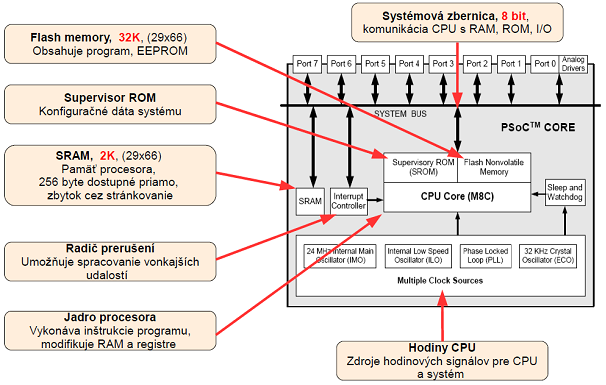

Na Obr. 2.1 sú zobrazené prvky architektúry jadra PSoC. Procesor je 8-bitový a dokáže spracovať až 4 milióny inštrukcií za sekundu. 8-bitová architektúra podporuje použitie až 64 kilobajtov pamäti Flash, v ktorej je uložená užívateľská aplikácia. Flash pamäť je „in-circuit programmable“, takže PSoC je možné programovať aj potom, ako je zapojený do dosky plošných spojov. Flash je zároveň aj „in-application programmable“, čo znamená, že mikroprocesor je schopný dynamicky meniť svoju vlastnú pamäť. Procesor je pripojený k viacerým digitálnym a analógovým blokom, ktoré poskytujú funkcionalitu a flexibilitu charakteristickú pre celú rodinu PSoC.

|

| Obr. 2.1 Jadro PSoC |

Registre procesora M8C

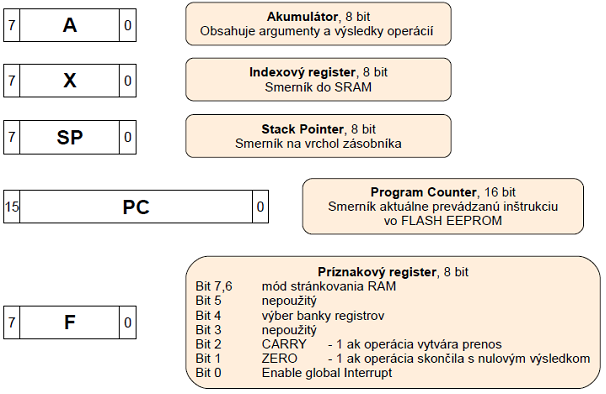

M8C je 8-bitový mikroprocesor MIPS harvardskej architektúry s voliteľnou hodinovou frekvenciou od 93.7 kHz do 24 MHz. Má päť vnútorných registrov, ktoré sú využívané pri vykonávaní programu.

|

| Obr. 2.2 Registre procesora M8C |

Štruktúra pamäte M8C

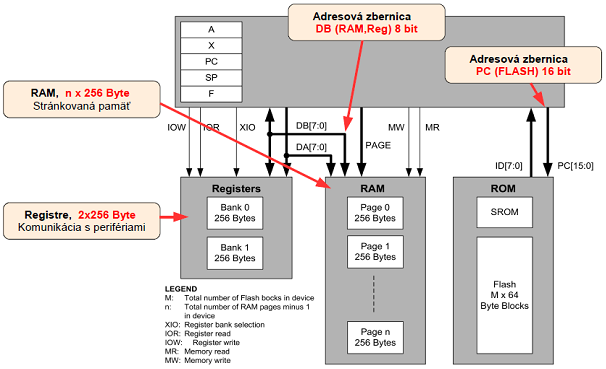

M8C má tri adresné priestory: ROM, RAM a registre. K adresnému priestoru ROM pristupujeme cez jeho vlastné adresy a dátovú zbernicu. ROM zahŕňa SROM a Flash pamäte. V pamäti Flash je uložený firmvér zariadenia a je rozdelená do 64-bajtových blokov. Používateľ nemusí ošetrovať prechod programu na ďalšiu pamäťovú stránku, pretože M8C automaticky zvyšuje 16-bitový register PC pri každej inštrukcii presahujúcej hranice aktuálnej stránky. V pamäti SROM je uložený program využívaný na spúšťanie PSoC, kalibrovanie obvodov a vykonávanie operácií s pamäťou Flash. Funkcie zabezpečované SROM sú volané z programu uloženého v pamäti Flash alebo pomocou programátora. Adresný priestor registrov je využívaný na konfigurovanie programovateľných blokov mikroprocesora. Skladá sa z dvoch 256-bajtových blokov. Na prepínanie medzi blokmi sa nastavuje bit XIO v registri F. Ak je F nastavený, zvolí sa blok1, ak nie je nastavený, zvolí sa blok0.

|

| Obr. 2.3 Adresný priestor |

Inštrukčné formáty

M8C má spolu sedem inštrukčných formátov, ktoré používajú inštrukcie o dĺžkach jeden, dva a tri bajty. Všetky bajty inštrukcie sú vyvolávané z programovej pamäte Flash, za použitia adries a dátovej zbernice, ktoré sú nezávislé od adries a dátovej zbernice používaných pre registre a prístup do pamäte RAM.

Digitálne a analógové bloky PSoC

Digitálne a analógové bloky sú moduly vytvorené z digitálnych a analógových prvkov, ktoré sú konfigurovateľné pre rôzne druhy operácií pomocou registrov špecifických pre každý blok.

Analógové bloky

Na rozdiel od digitálnych blokov, kde blok z užívateľského hľadiska vlastne predstavuje sústavu registrov v ktorých sa zvolí funkcia bloku, sú analógové bloky v podstate založené na obvodovom zapojení obsahujúce jeden operačný zosilovač (OZ) obklopený rôznymi, vo vnútri integrovanými, súčiastkami pripojovanými k OZ cez programovateľné spínače. Tie sú už ovládané nastavením bitov registrov bloku prístupné užívateľovi. Takto je možné u každého bloku definovať použité vstupy i spätné väzby. Analógové bloky: PGA, komparátory, ADC 6-14 bitov, rôzne konfigurácie, DAC 6-9 bitov.

Digitálne bloky

Digitálne bloky [2] redukujú potrebu použitia ďalších externých obvodov pre požadovanú funkcionalitu pripravovaného zariadenia. Sú určené na spracovávanie a generovanie hlavne digitálneho signálu. Dajú sa programovať a variovať tak, aby poskytovali funkčnosť štandardných elektronických integrovaných obvodov ako napríklad počítadlo, šírkový generátor pulzov, RS-232, IrDA, SPI, I2C príjem a binárnych dát, generátory pseudonáhodných čísel a iné. Taktiež sa používajú na prípravu požadovaného taktovacieho signálu pre analógové bloky, prípadne na spracovanie signálov z analógových blokov (možné prepojenie cez vstupno-výstupné piny). Ich činnosť je nezávislá na behu programu mikroprocesora, avšak môže byť moderovaná programom pomocou API funkcií.

Každý digitálny blok má priradených niekoľko registrov, ktorými sa nastavuje vnútorné zapojenie jeho obvodov a prepojenia s globálnou zbernicou. Tieto registre je možné meniť aj počas práce (za behu) mikroprocesora pomocou programu, a tým aj meniť funkčnosť a zapojenie blokov. Podrobná dokumentácia registrom je rozsiahla a voľne dostupná. Pre prácu s mikroprocesorom, kde za behu programu nedochádza k zmene štruktúry, nie je nutné registre detailne poznať, pretože o ich nastavenie sa postará grafický dizajnér, v ktorom sú už pred pripravené konfigurácie blokov na použitie pre niektoré základné zapojenia a funkcionality. Každé takéto zapojenie spotrebuje jeden alebo viac z blokov mikroprocesora.

Globálne vstupy a výstupy dodávajú digitálnym blokom možnosti na prepájanie taktovacích a dátových vstupov. Podobne ako digitálne bloky, aj globálne vstupy a výstupy sa nastavujú pomocou k nim prislúchajúceho registra. Podľa konfigurácie registra, jednotlivé bloky pripoja na 8 bitovú, globálnu, vstupnú zbernicu alebo 8 bitovú, globálnu, výstupnú zbernicu. K týmto zberniciam je možné pripojiť i vstupno-výstupné vývody mikroprocesoru.