Návrh hardvérovej časti dekodéra RC5-BIN: Rozdiel medzi revíziami

| Riadok 3: | Riadok 3: | ||

[[Kategória:Mechatronika]] | [[Kategória:Mechatronika]] | ||

{{Praca_uvod|2|Implementácia protokolu RC5 na platforme procesora Cypress|Protokol RC-5|Návrh hardvérovej časti dekodéra RC5-BIN|Implementácia dekodéra RC5-BIN v mikroprocesore Cypress||||||||||}} | {{Praca_uvod|2|Implementácia protokolu RC5 na platforme procesora Cypress|Protokol RC-5|Návrh hardvérovej časti dekodéra RC5-BIN|Implementácia dekodéra RC5-BIN v mikroprocesore Cypress||||||||||}} | ||

| − | = = | + | =Návrh hardvérovej časti dekódera RC5-BIN= |

| + | ==Cypress PSoC== | ||

| + | PSoC od spoločnosti Cypress predstavuje novú koncepciu mikroprocesorov <ref>http://www.psoc.cz/psoc-teoreticky-uvod.php</ref>, pretože okrem štandardných súčastí osem bitových procesorov obsahuje PSoC systém konfigurovateľných analógových a digitálnych blokov, na ktorých je možné vystavať množstvo ďalších prídavných digitálnych a analógových periférií. Digitálne konfigurovateľné bloky poskytujú základ pre výstavbu štandardných digitálnych periférií typu čítač , časovač, generátor náhodných čísiel, generátor CRC blokov UART, PWM(do slovníka cudz slov a skratiek) a mnoho ďalších. Naproti tomu analógové bloky poskytujú základ analógovým perifériám ako sú rôzne druhy analogovo-digitálnych, digitálno-analógových prevodníkov, operačných zosilňovačov, komparátorov a podobne. | ||

| + | Architektúra PSoC je zobrazená na Obr.2.1. | ||

| − | ... | + | [[Image:Obr2_1.jpg|Architektúra Cypress PSoC]] |

| + | Zdroj obrázku <ref>http://www.psoc.cz/psoc-teoreticky-uvod.php</ref> | ||

| + | |||

| + | Základné charakteristiky: | ||

| + | Najdôležitejšie vlastnosti mikroprocesora PSoC : | ||

| + | - voliteľné napätie 3.3 V alebo 5 V, | ||

| + | - možnosť napájacieho napätia nižšieho ako 1 V, | ||

| + | - programovateľná frekvencia, | ||

| + | - až 32 kB programovej pamäti, | ||

| + | - až 2 kB RAM, | ||

| + | - čítače a časovače s registrami 8, 16, 24 a 32 bitov, | ||

| + | - generátor CRC a pseudonáhodných sekvencií, | ||

| + | - dva plne duplexné bloky UART-u, | ||

| + | - bloky SPI, | ||

| + | - voliteľné zapojenie všetkých vstupno – výstupných pinov, | ||

| + | - voliteľná konfigurácia všetkých blokov, | ||

| + | - každý pin umožňuje nastavenie v riadení (Pull-Up, Pull-Down, High-Z, Open-Drain, Strong), | ||

| + | - možnosť generovať prerušenia po zmene logického stavu po ktoromkoľvek vstupno – výstupnom pine, | ||

| + | - referenčný zdroj hodinového signálu. | ||

| + | |||

| + | V nasledujúcich kapitolách budú popísané jednotlivé časti PSoC, ktoré boli využité pri implementácií protokolu RC-5. | ||

| + | ===Counter=== | ||

| + | Čítače poskytujú vlastnosť odčítania od nastavenej hodnoty periódy smerom k nule<ref>http://www.psoc.cz/psoc-moduly-timmer.php</ref>. Dĺžka periódy je voliteľná. Zdrojom hodín môže byť externý (riadiaci kryštál) alebo interný zdroj. Pokiaľ je činnosť čítača spustená, je nastavená perióda načítaná do čítacieho registra a s každou hranou hodín znížená smerom k nule. Počas odpočítavania je hodnota porovnávaná s tzv. komparačným registrom. V prípade zhody, alebo keď je hodnota čítača nižšia ako hodnota komparačného registra, je nastavená logická hodnota komparačného výstupu. Tento výstup môže byť vyvedený prostredníctvom vnútorných zberníc na ľubovoľný pin puzdra PSoC. Bloková schéma čítača je na Obr.2.2. | ||

| + | Základné vlastnosti : | ||

| + | - 8, 16, 24 alebo 32 – bitové univerzálne čítače, ktoré využívajú jeden, dva, tri alebo štyri PSoC digitálne bloky, | ||

| + | - zdroj hodín môže poskytovať frekvenciu až do 48 MHz, | ||

| + | - automatické opätovné načítanie periódy, | ||

| + | - programovateľná šírka impulzu, | ||

| + | - vstupy môžu zapínať alebo vypínať operácie čítača. | ||

| + | |||

| + | [[Image:counter.jpg|Bloková schéma čitača]] | ||

| + | Zdroj obrázku <ref>http://www.psoc.cz/psoc-moduly-timmer.php</ref> | ||

| + | |||

| + | ===UART=== | ||

| + | Používateľský blok UART (Universal Asynchronous Receiver Transmitter) je osem bitový univerzálny asynchrónny prijímač a vysielač, ktorý podporuje duplex RS-232 kompatibilitu, sériovú dátovú komunikácia skrz dva vodiče. Aplikačné programové rozhranie je vybavené rutinami firmvér na inicializáciu, konfiguráciu a ovládanie UART-u. Na Obr. 2.3 je znázornená bloková schéma PSoC bloku UART. | ||

| + | |||

| + | [[Image:UART.jpg|Bloková schéma UART]] | ||

| + | |||

| + | Zdroj obrázku<ref>CYPRESS, Semiconductor Corporation. PSoC Programmable System-on-Chip : Technical Reference Manual (TRM). San Jose, USA , c2008. 572 s. Document No. 001-14463 Rev. *C. Dostupný z WWW: <www.cypress.com></ref> | ||

| + | |||

| + | Základné vlastnosti : | ||

| + | - asynchrónny prijímač a vysielač | ||

| + | - dátový formát je kompatibilný so sériovým dátovým formátom RS-232 | ||

| + | - rýchlosť dátových dávok až do 6 Mbit za sekundu | ||

| + | - dátová štruktúra sa skladá zo štartu, voliteľnej parity a stop bitov | ||

| + | - voliteľné prerušenie pri naplnení prijímacieho registra a pri vyprázdnení odosielacieho registra | ||

| + | - vysoká úroveň prijímacích a vysielacích funkcií | ||

| + | |||

| + | Používateľský blok UART implementuje sériový prijímač a vysielač. UART zaberá dva digitálne PSoC bloky určených pre TX a RX v PSoC dizajnéri <ref>CYPRESS, Semiconductor Corporation. PSoC Programmable System-on-Chip : Technical Reference Manual (TRM). San Jose, USA , c2008. 572 s. Document No. 001-14463 Rev. *C. Dostupný z WWW: <www.cypress.com></ref>. PSoC blok TX poskytuje odosielaciu funkcionalitu a RX blok poskytuje prijímaciu funkcionalitu. RX a TX pracujú nezávisle. Každý z oboch blokov má vlastný kontrolný a stavový register, programovateľné prerušenia, vstupy a výstupy, register vyrovnávacej pamäte a posuvný register. Hodiny modulu využívajú obidva bloky TX aj RX. Frekvencia hodín musí byť nastavená na osemnásobnú hodnotu oproti žiadanej bitovej prenosovej rýchlosti hodnote. Blok UART je taktiež plne nastaviteľný v PSoC dizajnéri. | ||

| + | |||

| + | ===Digitálne vstupy a výstupy=== | ||

| + | Spojenie medzi mikroprocesorom PSoC a okolitým svetom je zaistený prostredníctvom vstupno – výstupných pinov. Operácie ako čítanie alebo zápis z pinu respektíve portu sú vykonávané veľmi podobne. Registre pre prístup k portu sú súčasťou adresného priestoru v pamäti RAM pod názvami PRT0DR, PRT1DR a PRT2DR [9]. | ||

| + | '''Nastavene portu''' | ||

| + | Zápis hodnoty do registra PRTxDR zaistí prostredníctvom inicializačného obvodu nastavenie požadovaných stavov na porte. Inicializačný obvod prenesie hodnotu z registra na port priamo (v režime STRONG), cez PULL-UP, PULL-DOWN alebo otvorený kolektor. | ||

| + | '''Čítanie portu''' | ||

| + | Prečítaním hodnoty PRTxDR je prenesený logický stav na portoch do registru A. V prípade, že je pripojený na port externý obvod, napríklad tlačidlo, môže sa líšiť prečítaná hodnota (A) od nastavenej (PRTxDR). | ||

| + | '''Riadenie portu''' | ||

| + | Nastavenie spôsobu, akým bude inicializačný obvod prenášať hodnotu registra PRTxDR na porty je nastavované vizuálne vo vývojovom prostredí alebo manuálne zápisom do banky PRTxDM2, PRTxDM1 a PRTxDM0. Existuje celkom osem možností ako porty inicializovať. Druh použitej inicializácie závisí na pripojených externých komponentoch. Nasledujúca tabuľka v stručnosti opisuje rôzne režimy portu. | ||

| + | |||

| + | <references/> | ||

Verzia zo dňa a času 17:36, 22. jún 2010

| 1. | Protokol RC-5 |

| 2. | Návrh hardvérovej časti dekodéra RC5-BIN |

| 3. | Implementácia dekodéra RC5-BIN v mikroprocesore Cypress

|

Obsah

Návrh hardvérovej časti dekódera RC5-BIN

Cypress PSoC

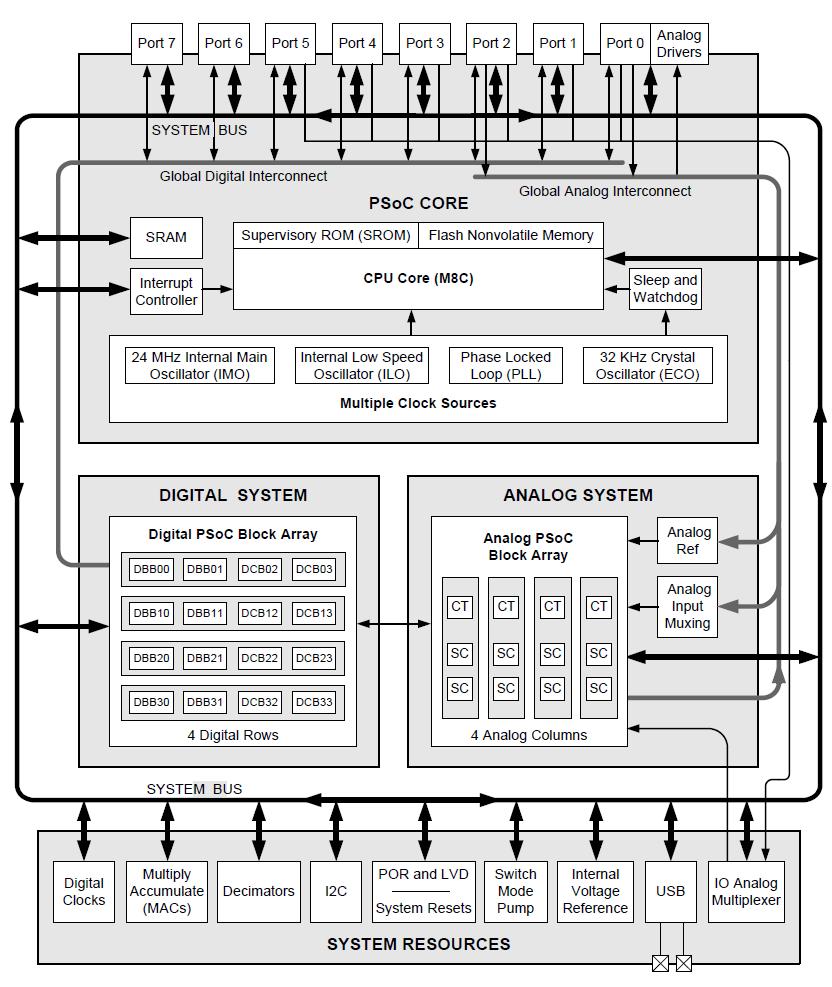

PSoC od spoločnosti Cypress predstavuje novú koncepciu mikroprocesorov [1], pretože okrem štandardných súčastí osem bitových procesorov obsahuje PSoC systém konfigurovateľných analógových a digitálnych blokov, na ktorých je možné vystavať množstvo ďalších prídavných digitálnych a analógových periférií. Digitálne konfigurovateľné bloky poskytujú základ pre výstavbu štandardných digitálnych periférií typu čítač , časovač, generátor náhodných čísiel, generátor CRC blokov UART, PWM(do slovníka cudz slov a skratiek) a mnoho ďalších. Naproti tomu analógové bloky poskytujú základ analógovým perifériám ako sú rôzne druhy analogovo-digitálnych, digitálno-analógových prevodníkov, operačných zosilňovačov, komparátorov a podobne. Architektúra PSoC je zobrazená na Obr.2.1.

Zdroj obrázku [2]

Zdroj obrázku [2]

Základné charakteristiky: Najdôležitejšie vlastnosti mikroprocesora PSoC : - voliteľné napätie 3.3 V alebo 5 V, - možnosť napájacieho napätia nižšieho ako 1 V, - programovateľná frekvencia, - až 32 kB programovej pamäti, - až 2 kB RAM, - čítače a časovače s registrami 8, 16, 24 a 32 bitov, - generátor CRC a pseudonáhodných sekvencií, - dva plne duplexné bloky UART-u, - bloky SPI, - voliteľné zapojenie všetkých vstupno – výstupných pinov, - voliteľná konfigurácia všetkých blokov, - každý pin umožňuje nastavenie v riadení (Pull-Up, Pull-Down, High-Z, Open-Drain, Strong), - možnosť generovať prerušenia po zmene logického stavu po ktoromkoľvek vstupno – výstupnom pine, - referenčný zdroj hodinového signálu.

V nasledujúcich kapitolách budú popísané jednotlivé časti PSoC, ktoré boli využité pri implementácií protokolu RC-5.

Counter

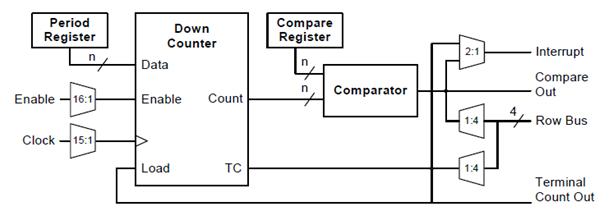

Čítače poskytujú vlastnosť odčítania od nastavenej hodnoty periódy smerom k nule[3]. Dĺžka periódy je voliteľná. Zdrojom hodín môže byť externý (riadiaci kryštál) alebo interný zdroj. Pokiaľ je činnosť čítača spustená, je nastavená perióda načítaná do čítacieho registra a s každou hranou hodín znížená smerom k nule. Počas odpočítavania je hodnota porovnávaná s tzv. komparačným registrom. V prípade zhody, alebo keď je hodnota čítača nižšia ako hodnota komparačného registra, je nastavená logická hodnota komparačného výstupu. Tento výstup môže byť vyvedený prostredníctvom vnútorných zberníc na ľubovoľný pin puzdra PSoC. Bloková schéma čítača je na Obr.2.2. Základné vlastnosti : - 8, 16, 24 alebo 32 – bitové univerzálne čítače, ktoré využívajú jeden, dva, tri alebo štyri PSoC digitálne bloky, - zdroj hodín môže poskytovať frekvenciu až do 48 MHz, - automatické opätovné načítanie periódy, - programovateľná šírka impulzu, - vstupy môžu zapínať alebo vypínať operácie čítača.

Zdroj obrázku [4]

Zdroj obrázku [4]

UART

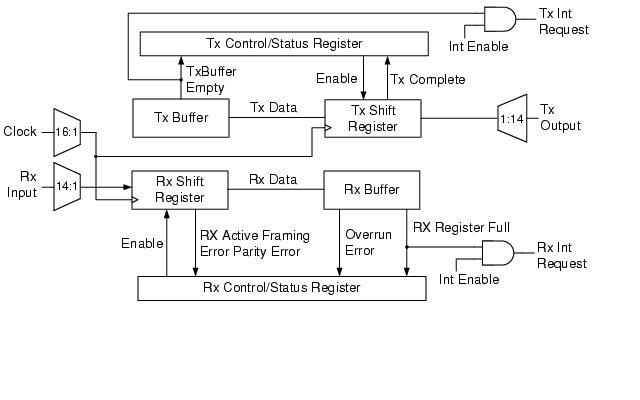

Používateľský blok UART (Universal Asynchronous Receiver Transmitter) je osem bitový univerzálny asynchrónny prijímač a vysielač, ktorý podporuje duplex RS-232 kompatibilitu, sériovú dátovú komunikácia skrz dva vodiče. Aplikačné programové rozhranie je vybavené rutinami firmvér na inicializáciu, konfiguráciu a ovládanie UART-u. Na Obr. 2.3 je znázornená bloková schéma PSoC bloku UART.

Zdroj obrázku[5]

Základné vlastnosti : - asynchrónny prijímač a vysielač - dátový formát je kompatibilný so sériovým dátovým formátom RS-232 - rýchlosť dátových dávok až do 6 Mbit za sekundu - dátová štruktúra sa skladá zo štartu, voliteľnej parity a stop bitov - voliteľné prerušenie pri naplnení prijímacieho registra a pri vyprázdnení odosielacieho registra - vysoká úroveň prijímacích a vysielacích funkcií

Používateľský blok UART implementuje sériový prijímač a vysielač. UART zaberá dva digitálne PSoC bloky určených pre TX a RX v PSoC dizajnéri [6]. PSoC blok TX poskytuje odosielaciu funkcionalitu a RX blok poskytuje prijímaciu funkcionalitu. RX a TX pracujú nezávisle. Každý z oboch blokov má vlastný kontrolný a stavový register, programovateľné prerušenia, vstupy a výstupy, register vyrovnávacej pamäte a posuvný register. Hodiny modulu využívajú obidva bloky TX aj RX. Frekvencia hodín musí byť nastavená na osemnásobnú hodnotu oproti žiadanej bitovej prenosovej rýchlosti hodnote. Blok UART je taktiež plne nastaviteľný v PSoC dizajnéri.

Digitálne vstupy a výstupy

Spojenie medzi mikroprocesorom PSoC a okolitým svetom je zaistený prostredníctvom vstupno – výstupných pinov. Operácie ako čítanie alebo zápis z pinu respektíve portu sú vykonávané veľmi podobne. Registre pre prístup k portu sú súčasťou adresného priestoru v pamäti RAM pod názvami PRT0DR, PRT1DR a PRT2DR [9]. Nastavene portu Zápis hodnoty do registra PRTxDR zaistí prostredníctvom inicializačného obvodu nastavenie požadovaných stavov na porte. Inicializačný obvod prenesie hodnotu z registra na port priamo (v režime STRONG), cez PULL-UP, PULL-DOWN alebo otvorený kolektor. Čítanie portu Prečítaním hodnoty PRTxDR je prenesený logický stav na portoch do registru A. V prípade, že je pripojený na port externý obvod, napríklad tlačidlo, môže sa líšiť prečítaná hodnota (A) od nastavenej (PRTxDR). Riadenie portu Nastavenie spôsobu, akým bude inicializačný obvod prenášať hodnotu registra PRTxDR na porty je nastavované vizuálne vo vývojovom prostredí alebo manuálne zápisom do banky PRTxDM2, PRTxDM1 a PRTxDM0. Existuje celkom osem možností ako porty inicializovať. Druh použitej inicializácie závisí na pripojených externých komponentoch. Nasledujúca tabuľka v stručnosti opisuje rôzne režimy portu.

- ↑ http://www.psoc.cz/psoc-teoreticky-uvod.php

- ↑ http://www.psoc.cz/psoc-teoreticky-uvod.php

- ↑ http://www.psoc.cz/psoc-moduly-timmer.php

- ↑ http://www.psoc.cz/psoc-moduly-timmer.php

- ↑ CYPRESS, Semiconductor Corporation. PSoC Programmable System-on-Chip : Technical Reference Manual (TRM). San Jose, USA , c2008. 572 s. Document No. 001-14463 Rev. *C. Dostupný z WWW: <www.cypress.com>

- ↑ CYPRESS, Semiconductor Corporation. PSoC Programmable System-on-Chip : Technical Reference Manual (TRM). San Jose, USA , c2008. 572 s. Document No. 001-14463 Rev. *C. Dostupný z WWW: <www.cypress.com>