Prehľad architektúry PSoC: Rozdiel medzi revíziami

d |

|||

| (18 medziľahlých úprav od 3 ďalších používateľov nie je zobrazených) | |||

| Riadok 1: | Riadok 1: | ||

| − | Mikroprocesory PSoC (Programmable System on Chip – Programovateľný systém na čipe) sa skladajú z konfigurovateľných blokov analógových obvodov a digitálnej logiky, ktoré sú vzájomne programovo prepojené. Uvedená architektúra umožňuje vytvárať zákaznícke konfigurácie mikroprocesora tak, aby boli splnené požiadavky potrebné na realizáciu jednotlivých aplikácií. Bloková schéma na Obr. 1.1 zobrazuje architektúru celej rodiny mikroprocesorov PSoC. | + | [[Kategória:Konfigurovateľné mikroprocesorové systémy]] |

| + | [[Kategória:Úvod do technológie PSoC ]] | ||

| + | __NOTOC__ | ||

| + | {{sablona_mikroprocoserove_systemy|Úvod do technológie PSoC|Prehľad architektúry PSoC|Elektrické a mechanické parametre architektúry PSoC|Vývojové prostredie pre systémy PSoC}} | ||

| + | '''Mikroprocesory PSoC''' <ref>http://www.cypress.com</ref> (Programmable System on Chip – Programovateľný systém na čipe) sa skladajú z konfigurovateľných blokov analógových obvodov a digitálnej logiky, ktoré sú vzájomne programovo prepojené. Uvedená architektúra umožňuje vytvárať zákaznícke konfigurácie mikroprocesora tak, aby boli splnené požiadavky potrebné na realizáciu jednotlivých aplikácií. Bloková schéma na Obr. 1.1 zobrazuje architektúru celej rodiny mikroprocesorov PSoC. | ||

== Vnútorná štruktúra PSoC == | == Vnútorná štruktúra PSoC == | ||

| − | Spoločnosť Cypress vyvinula niekoľko desiatok typov súčiastok typov PSoC. Líšia sa predovšetkým množstvom a druhom blokov, veľkosťou pamäti programu (FLASH), pamäťou dát (RAM), veľkosťou a druhom puzdier a ďalšími parametrami. V závislosti na type obsahujú 4-16 digitálnych a 3-12 analógových blokov. | + | Spoločnosť '''Cypress''' vyvinula niekoľko desiatok typov súčiastok typov PSoC. Líšia sa predovšetkým množstvom a druhom blokov, veľkosťou pamäti programu ([http://sk.wikipedia.org/wiki/FLASH FLASH]), pamäťou dát ([http://sk.wikipedia.org/wiki/Pam%C3%A4%C5%A5_s_priamym_pr%C3%ADstupom RAM]), veľkosťou a druhom puzdier a ďalšími parametrami. V závislosti na type obsahujú 4-16 digitálnych a 3-12 analógových blokov. |

| − | [[Image:Pagac_struktura.png|center|Obr. 1.1 Vnútorná štruktúra PSoC | + | <center> |

| + | {|class="wikitable" | ||

| + | | align="center" | [[Image:Pagac_struktura.png]] | ||

| + | |- | ||

| + | | align="center" | Obr. 1.1 Vnútorná štruktúra PSoC | ||

| + | |} | ||

| + | </center> | ||

| + | == M8C – procesorové jadro == | ||

| + | |||

| + | Na Obr. 2.1 sú zobrazené prvky architektúry jadra PSoC. Procesor je 8-bitový a dokáže spracovať až 4 milióny inštrukcií za sekundu. | ||

| + | 8-bitová architektúra podporuje použitie až 64 kilobajtov pamäti Flash, v ktorej je uložená užívateľská aplikácia. Flash pamäť je „in-circuit programmable“, takže PSoC je možné programovať aj potom, ako je zapojený do dosky plošných spojov. Flash je zároveň aj „in-application programmable“, čo znamená, že mikroprocesor je schopný dynamicky meniť svoju vlastnú pamäť. [http://sk.wikipedia.org/wiki/Procesor Procesor] je pripojený k viacerým digitálnym a analógovým blokom, ktoré poskytujú funkcionalitu a flexibilitu charakteristickú pre celú rodinu PSoC. | ||

| + | |||

| + | <center> | ||

| + | {|class="wikitable" | ||

| + | | align="center" | [[Image:Pagac_JadroPSoC.png]] | ||

| + | |- | ||

| + | | align="center" | Obr. 2.1 Jadro PSoC | ||

| + | |} | ||

| + | </center> | ||

| + | |||

| + | === Registre procesora M8C === | ||

| − | == M8C | + | '''M8C''' je 8-bitový [http://sk.wikipedia.org/wiki/Mikroprocesor mikroprocesor] MIPS harvardskej architektúry s voliteľnou hodinovou frekvenciou od 93.7 kHz do 24 MHz. Má päť vnútorných [http://sk.wikipedia.org/wiki/Register_(procesor) registrov], ktoré sú využívané pri vykonávaní programu. |

| + | |||

| + | <center> | ||

| + | {|class="wikitable" | ||

| + | | align="center" | [[Image:Pagac_registreprocesora.png]] | ||

| + | |- | ||

| + | | align="center" | Obr. 2.2 Registre procesora M8C | ||

| + | |} | ||

| + | </center> | ||

| + | |||

| + | === Štruktúra pamäte M8C === | ||

| + | |||

| + | M8C má tri adresné priestory: [http://sk.wikipedia.org/wiki/ROM ROM], RAM a registre. K adresnému priestoru ROM pristupujeme cez jeho vlastné adresy a dátovú [http://sk.wikipedia.org/wiki/Zbernica#Zbernica_po.C4.8D.C3.ADta.C4.8Da zbernicu]. ROM zahŕňa SROM a Flash pamäte. V pamäti Flash je uložený firmvér zariadenia a je rozdelená do 64-bajtových blokov. Používateľ nemusí ošetrovať prechod programu na ďalšiu pamäťovú stránku, pretože M8C automaticky zvyšuje 16-bitový register PC pri každej inštrukcii presahujúcej hranice aktuálnej stránky. V pamäti SROM je uložený program využívaný na spúšťanie PSoC, kalibrovanie obvodov a vykonávanie operácií s pamäťou Flash. Funkcie zabezpečované SROM sú volané z programu uloženého v pamäti Flash alebo pomocou programátora. Adresný priestor registrov je využívaný na konfigurovanie programovateľných blokov mikroprocesora. Skladá sa z dvoch 256-bajtových blokov. Na prepínanie medzi blokmi sa nastavuje bit XIO v registri F. Ak je F nastavený, zvolí sa blok1, ak nie je nastavený, zvolí sa blok0. | ||

| + | |||

| + | <center> | ||

| + | {|class="wikitable" | ||

| + | | align="center" | [[Image:Pagac_adresnypriestor.png]] | ||

| + | |- | ||

| + | | align="center" | Obr. 2.3 Adresný priestor | ||

| + | |} | ||

| + | </center> | ||

| + | |||

| + | === Inštrukčné formáty === | ||

| + | |||

| + | M8C má spolu sedem inštrukčných formátov, ktoré používajú inštrukcie o dĺžkach jeden, dva a tri bajty. Všetky bajty inštrukcie sú vyvolávané z programovej pamäte Flash, za použitia adries a dátovej zbernice, ktoré sú nezávislé od adries a dátovej zbernice používaných pre registre a prístup do pamäte RAM. | ||

| − | + | == Digitálne a analógové bloky PSoC == | |

| − | |||

| − | + | '''Digitálne a analógové bloky sú moduly''' vytvorené z digitálnych a analógových prvkov, ktoré sú konfigurovateľné pre rôzne druhy operácií pomocou registrov špecifických pre každý blok. | |

| − | == | + | === Digitálne bloky === |

| − | + | '''Digitálne bloky''' <ref>http://www.lubino.sk/rs/3/files/diplomka_-_ubo.pdf</ref> redukujú potrebu použitia ďalších externých obvodov pre požadovanú funkcionalitu pripravovaného zariadenia. Sú určené na spracovávanie a generovanie hlavne digitálneho signálu. Dajú sa programovať a variovať tak, aby poskytovali funkčnosť štandardných elektronických integrovaných obvodov ako napríklad počítadlo, šírkový generátor pulzov, RS-232, IrDA, SPI, I2C príjem a binárnych dát, generátory pseudonáhodných čísel a iné. Taktiež sa používajú na prípravu požadovaného taktovacieho signálu pre analógové bloky, prípadne na spracovanie signálov z analógových blokov (možné prepojenie cez vstupno-výstupné piny). Ich činnosť je nezávislá na behu programu mikroprocesora, avšak môže byť moderovaná programom pomocou [http://sk.wikipedia.org/wiki/Application_programming_interface API] funkcií. | |

| − | [[ | + | * PWMs (8 to 32 bit) |

| + | * [http://www.cypress.com/?docID=19560 PWMs with Dead band (8 to 32 bit)] | ||

| + | * [http://www.cypress.com/?docID=19121 Counters (8 to 32 bit)] | ||

| + | * [http://www.cypress.com/?docID=19152 Timers (8 to 32 bit)] | ||

| + | * [http://www.cypress.com/?docID=19130 UART 8 bit with selectable parity (up to 2)] | ||

| + | * [http://www.cypress.com/?docID=19104 SPI slave and master (up to 2)] | ||

| + | * [http://www.cypress.com/?docID=20823 I2C slave and multi-master (1 available as a System Resource)] | ||

| + | * [http://www.cypress.com/?docID=16559 Cyclical Redundancy Checker/Generator (8 to 32 bit)] | ||

| + | * [http://www.cypress.com/?docID=19131 IrDA (up to 2)] | ||

| + | * [http://www.cypress.com/?docID=19082 Pseudo Random Sequence Generators (8 to 32 bit)] | ||

| − | == | + | === Analógové bloky === |

| − | + | '''Analógové bloky''' <ref>http://www.lubino.sk/rs/3/files/diplomka_-_ubo.pdf</ref> sú taktiež zdrojom prostriedkov pre aplikácie, avšak orientované na spracovávanie a generovanie analógových signálov. Základom analógových blokov sú obvody spínače, prepínače, operačné zosilňovače a spínané kondenzátory. Každý analógový obvod ma viac potenciálne použiteľných vstupov a výstupov. K dispozícii sú vždy tieto tri výstupy: | |

| + | * analógová výstupná zbernica (ABUS) | ||

| + | * porovnávacia zbernica (CBUS) | ||

| + | * výstupná zbernica (OUT) | ||

| − | + | Zoznam analógových blokov: | |

| + | * Analog-to-digital converters (up to 4, with 6- to 14-bit resolution, selectable as Incremental, Delta Sigma, and SAR) | ||

| + | * Filters (2, 4, 6, and 8 pole band-pass, low-pass, and notch) | ||

| + | * Amplifiers (up to 4, with selectable gain to 48x) | ||

| + | * [http://www.cypress.com/?docID=16708 Instrumentation amplifiers (up to 2, with selectable gain to 93x)] | ||

| + | * Comparators (up to 4, with 16 selectable thresholds) | ||

| + | * DACs (up to 4, with 6- to 9-bit resolution) | ||

| + | * Multiplying DACs (up to 4, with 6- to 9-bit resolution) | ||

| + | * High current output drivers (four with 30 mA drive as a Core Resource) | ||

| + | * 1.3V reference (as a System Resource) | ||

| + | * [http://www.cypress.com/?docID=17257 DTMF Dialer] | ||

| + | * Modulators | ||

| + | * Correlators | ||

| + | * Peak detectors | ||

| + | * Many other topologies possible | ||

| − | + | Analógová výstupná zbernica je vodičom analógového signálu. Túto zbernicu spolu zdieľajú analógové bloky v jednom stĺpci. Keďže je takýchto stĺpcov viac, je viac aj zberníc tohoto typu. Vo väčšine modelov mikroprocesora sú 4. K tejto zbernici je pripojený analógový výstupný zásobník (Analog Output Buffer), ktorý v závislosti od nastavenia prepojí zbernicu s nastaveným analógovým výstupným pinom. Porovnávacia zbernica je digitálnou zbernicou a taktiež ju zdieľajú všetky analógové bloky v jednom stĺpci. Túto zbernicu nie je možné pripojiť na vstupno-výstupný pin, ale je možné pripojiť ju na vstup niektorého digitálneho bloku. Podobne aj výstupná zbernica je zdieľaná vrámci jedného stĺpca. | |

| − | + | <references/> | |

| − | |||

Aktuálna revízia z 09:41, 21. marec 2013

| Predmet |

|

|---|---|

| Konfigurovateľné mikroprocesorové systémy | |

| Tématická časť: | |

| Úvod do technológie PSoC |

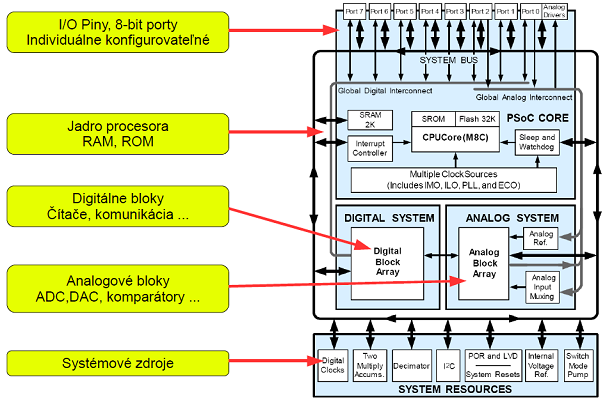

Mikroprocesory PSoC [1] (Programmable System on Chip – Programovateľný systém na čipe) sa skladajú z konfigurovateľných blokov analógových obvodov a digitálnej logiky, ktoré sú vzájomne programovo prepojené. Uvedená architektúra umožňuje vytvárať zákaznícke konfigurácie mikroprocesora tak, aby boli splnené požiadavky potrebné na realizáciu jednotlivých aplikácií. Bloková schéma na Obr. 1.1 zobrazuje architektúru celej rodiny mikroprocesorov PSoC.

Vnútorná štruktúra PSoC

Spoločnosť Cypress vyvinula niekoľko desiatok typov súčiastok typov PSoC. Líšia sa predovšetkým množstvom a druhom blokov, veľkosťou pamäti programu (FLASH), pamäťou dát (RAM), veľkosťou a druhom puzdier a ďalšími parametrami. V závislosti na type obsahujú 4-16 digitálnych a 3-12 analógových blokov.

|

| Obr. 1.1 Vnútorná štruktúra PSoC |

M8C – procesorové jadro

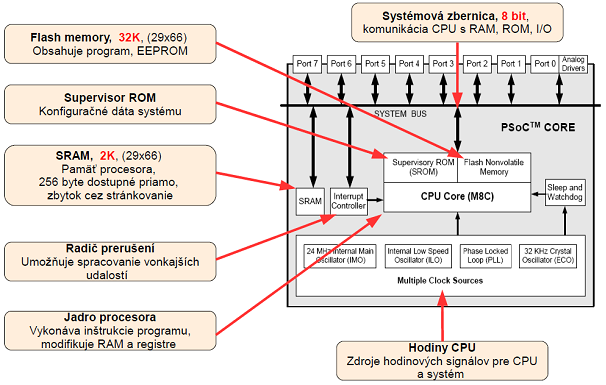

Na Obr. 2.1 sú zobrazené prvky architektúry jadra PSoC. Procesor je 8-bitový a dokáže spracovať až 4 milióny inštrukcií za sekundu. 8-bitová architektúra podporuje použitie až 64 kilobajtov pamäti Flash, v ktorej je uložená užívateľská aplikácia. Flash pamäť je „in-circuit programmable“, takže PSoC je možné programovať aj potom, ako je zapojený do dosky plošných spojov. Flash je zároveň aj „in-application programmable“, čo znamená, že mikroprocesor je schopný dynamicky meniť svoju vlastnú pamäť. Procesor je pripojený k viacerým digitálnym a analógovým blokom, ktoré poskytujú funkcionalitu a flexibilitu charakteristickú pre celú rodinu PSoC.

|

| Obr. 2.1 Jadro PSoC |

Registre procesora M8C

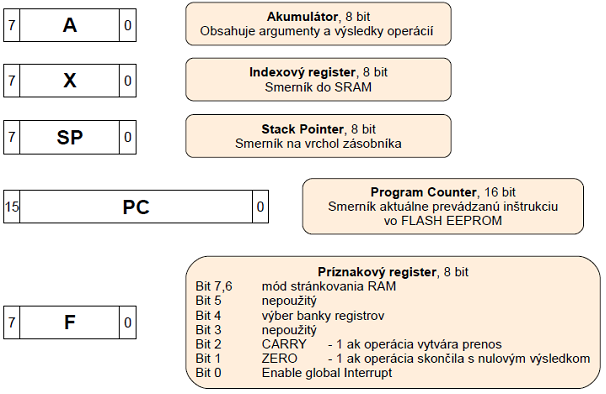

M8C je 8-bitový mikroprocesor MIPS harvardskej architektúry s voliteľnou hodinovou frekvenciou od 93.7 kHz do 24 MHz. Má päť vnútorných registrov, ktoré sú využívané pri vykonávaní programu.

|

| Obr. 2.2 Registre procesora M8C |

Štruktúra pamäte M8C

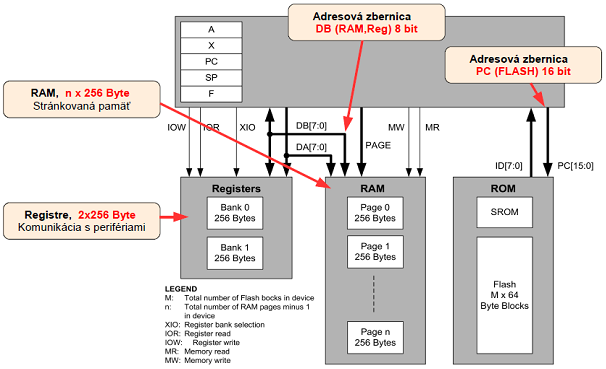

M8C má tri adresné priestory: ROM, RAM a registre. K adresnému priestoru ROM pristupujeme cez jeho vlastné adresy a dátovú zbernicu. ROM zahŕňa SROM a Flash pamäte. V pamäti Flash je uložený firmvér zariadenia a je rozdelená do 64-bajtových blokov. Používateľ nemusí ošetrovať prechod programu na ďalšiu pamäťovú stránku, pretože M8C automaticky zvyšuje 16-bitový register PC pri každej inštrukcii presahujúcej hranice aktuálnej stránky. V pamäti SROM je uložený program využívaný na spúšťanie PSoC, kalibrovanie obvodov a vykonávanie operácií s pamäťou Flash. Funkcie zabezpečované SROM sú volané z programu uloženého v pamäti Flash alebo pomocou programátora. Adresný priestor registrov je využívaný na konfigurovanie programovateľných blokov mikroprocesora. Skladá sa z dvoch 256-bajtových blokov. Na prepínanie medzi blokmi sa nastavuje bit XIO v registri F. Ak je F nastavený, zvolí sa blok1, ak nie je nastavený, zvolí sa blok0.

|

| Obr. 2.3 Adresný priestor |

Inštrukčné formáty

M8C má spolu sedem inštrukčných formátov, ktoré používajú inštrukcie o dĺžkach jeden, dva a tri bajty. Všetky bajty inštrukcie sú vyvolávané z programovej pamäte Flash, za použitia adries a dátovej zbernice, ktoré sú nezávislé od adries a dátovej zbernice používaných pre registre a prístup do pamäte RAM.

Digitálne a analógové bloky PSoC

Digitálne a analógové bloky sú moduly vytvorené z digitálnych a analógových prvkov, ktoré sú konfigurovateľné pre rôzne druhy operácií pomocou registrov špecifických pre každý blok.

Digitálne bloky

Digitálne bloky [2] redukujú potrebu použitia ďalších externých obvodov pre požadovanú funkcionalitu pripravovaného zariadenia. Sú určené na spracovávanie a generovanie hlavne digitálneho signálu. Dajú sa programovať a variovať tak, aby poskytovali funkčnosť štandardných elektronických integrovaných obvodov ako napríklad počítadlo, šírkový generátor pulzov, RS-232, IrDA, SPI, I2C príjem a binárnych dát, generátory pseudonáhodných čísel a iné. Taktiež sa používajú na prípravu požadovaného taktovacieho signálu pre analógové bloky, prípadne na spracovanie signálov z analógových blokov (možné prepojenie cez vstupno-výstupné piny). Ich činnosť je nezávislá na behu programu mikroprocesora, avšak môže byť moderovaná programom pomocou API funkcií.

- PWMs (8 to 32 bit)

- PWMs with Dead band (8 to 32 bit)

- Counters (8 to 32 bit)

- Timers (8 to 32 bit)

- UART 8 bit with selectable parity (up to 2)

- SPI slave and master (up to 2)

- I2C slave and multi-master (1 available as a System Resource)

- Cyclical Redundancy Checker/Generator (8 to 32 bit)

- IrDA (up to 2)

- Pseudo Random Sequence Generators (8 to 32 bit)

Analógové bloky

Analógové bloky [3] sú taktiež zdrojom prostriedkov pre aplikácie, avšak orientované na spracovávanie a generovanie analógových signálov. Základom analógových blokov sú obvody spínače, prepínače, operačné zosilňovače a spínané kondenzátory. Každý analógový obvod ma viac potenciálne použiteľných vstupov a výstupov. K dispozícii sú vždy tieto tri výstupy:

- analógová výstupná zbernica (ABUS)

- porovnávacia zbernica (CBUS)

- výstupná zbernica (OUT)

Zoznam analógových blokov:

- Analog-to-digital converters (up to 4, with 6- to 14-bit resolution, selectable as Incremental, Delta Sigma, and SAR)

- Filters (2, 4, 6, and 8 pole band-pass, low-pass, and notch)

- Amplifiers (up to 4, with selectable gain to 48x)

- Instrumentation amplifiers (up to 2, with selectable gain to 93x)

- Comparators (up to 4, with 16 selectable thresholds)

- DACs (up to 4, with 6- to 9-bit resolution)

- Multiplying DACs (up to 4, with 6- to 9-bit resolution)

- High current output drivers (four with 30 mA drive as a Core Resource)

- 1.3V reference (as a System Resource)

- DTMF Dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analógová výstupná zbernica je vodičom analógového signálu. Túto zbernicu spolu zdieľajú analógové bloky v jednom stĺpci. Keďže je takýchto stĺpcov viac, je viac aj zberníc tohoto typu. Vo väčšine modelov mikroprocesora sú 4. K tejto zbernici je pripojený analógový výstupný zásobník (Analog Output Buffer), ktorý v závislosti od nastavenia prepojí zbernicu s nastaveným analógovým výstupným pinom. Porovnávacia zbernica je digitálnou zbernicou a taktiež ju zdieľajú všetky analógové bloky v jednom stĺpci. Túto zbernicu nie je možné pripojiť na vstupno-výstupný pin, ale je možné pripojiť ju na vstup niektorého digitálneho bloku. Podobne aj výstupná zbernica je zdieľaná vrámci jedného stĺpca.